# Apontamentos Teóricos da Disciplina de SISTEMAS DIGITAIS 1

Licenciatura em Engenharia de Sistemas e Informática

2º Ano -- 2º Semestre

# **António Joaquim Esteves João Miguel Fernandes**

Departamento de Informática

**ESCOLA DE ENGENHARIA**

### Universidade do Minho

Março 2006

## ÍNDICE

| 1. | Introdução                              | 3   |

|----|-----------------------------------------|-----|

| 2. | Álgebra Booleana                        | 9   |

| 3. | Conceitos sobre Sistemas Combinacionais | 21  |

| 4. | VHDL                                    | 42  |

| 5. | Aplicação de Sistemas Combinacionais    | 64  |

| 6. | Conceitos sobre Sistemas Sequenciais    | 89  |

| 7. | Aplicação de Sistemas Sequenciais       | 116 |

| 8. | Dispositivos Programáveis e Memórias    | 127 |

| 9. | Bibliografia                            | 147 |

#### 1. Introdução

#### 1.1. Sistemas digitais vs. analógicos

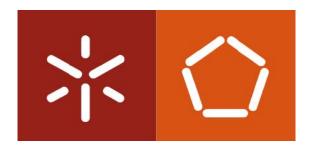

Um <u>sistema</u> é um conjunto de partes relacionadas que funcionam como um todo para atingir um determinado objectivo. Um <u>sistema</u> possui entradas e saídas e apresenta um comportamento definido à custa de funções que convertem as entradas em saídas. Um <u>sistema analógico</u> processa sinais que variam ao longo do tempo e que podem assumir qualquer valor dum intervalo contínuo de tensão, corrente, pressão, ... O mesmo se aplica ao <u>sistema digital</u>: a diferença está em nós desejarmos que isso não aconteça.

A vantagem mais importante dos sistemas digitais é a sua capacidade para operarem com sinais eléctricos que tenham sido degradados. Pelo facto de as saídas serem discretas, uma ligeira variação numa entrada continua a ser interpretada correctamente. Nos circuitos analógicos, um ligeiro erro na entrada provoca um erro na saída. O <u>sistema binário</u> é a forma mais simples de sistema digital. Um <u>sinal binário</u> é modelado de forma a que ele apenas assuma dois valores discretos: 0 ou 1, Baixo/LOW ou Alto/HIGH, Falso ou Verdadeiro.

#### 1.2. Abstracção digital

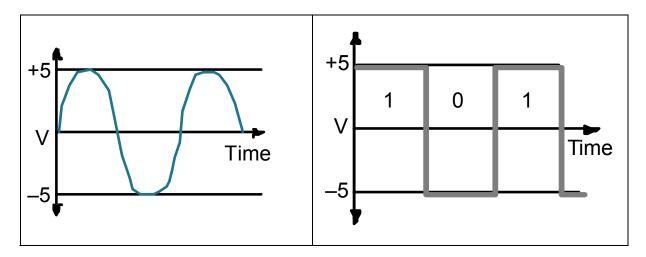

Os circuitos digitais operam sobre tensões e correntes analógicas. A <u>abstracção</u> <u>digital</u> consiste em ignorar comportamento analógico na maior parte das situações, permitindo deste modo que os circuitos sejam modelados como se eles processassem apenas 0s e 1s.

Associação entre um intervalo de valores analógicos e cada um dos valores lógicos (0 e 1). À diferença entre os limites desses intervalos chama-se margem de ruído.

#### 1.3. Sistemas síncronos vs. assíncronos

Um <u>sistema síncrono</u> é aquele em que os elementos mudam o seu valor em determinados instantes específicos. Um <u>sistema assíncrono</u> possui saídas que podem mudar de valor em qualquer instante. Por exemplo, considere-se um relógio digital com alarme, programado para tocar às 13:59. Num sistema síncrono, as saídas (HH, mm, ...) mudam todas ao mesmo tempo:  $12:59 \rightarrow 13:00 \rightarrow 13:01 \rightarrow ...$  Num sistema assíncrono, as saídas não têm forçosamente que mudar em simultâneo:  $12:59 \rightarrow 13:59 \rightarrow 13:00 \rightarrow ...$

#### 1.4. Portas lógicas (gates)

As portas lógicas são o dispositivo digital mais elementar. Uma <u>porta lógica</u> possui uma ou mais entradas e gera uma saída que é uma função dos valores actuais das entradas. Uma porta lógica é um <u>circuito combinacional</u> porque as saídas dependem exclusivamente da combinação actual das entradas.

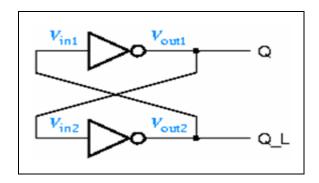

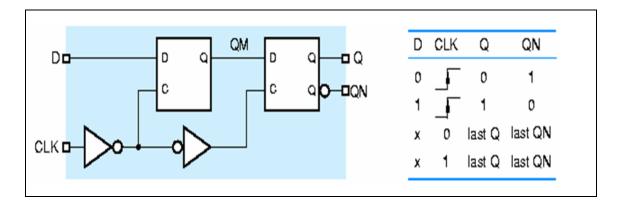

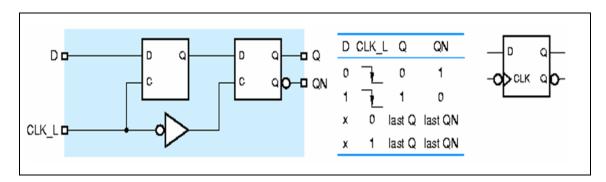

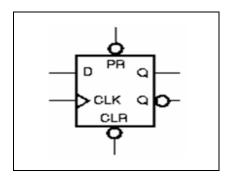

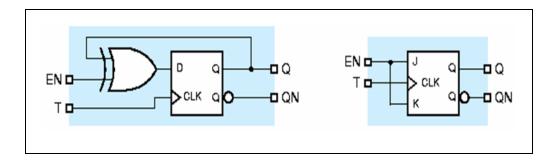

#### 1.5. Flip-flops

Um <u>flip-flop</u> é um dispositivo que guarda um 0 ou um 1 na saída. O <u>estado</u> do flip-flop é o valor que ele guarda no presente instante. O valor guardado só pode ser alterado em determinados instantes, impostos por uma entrada de relógio (<u>clock</u>). Um circuito digital que inclui flip-flops é um <u>circuito sequencial</u>. A saída dum circuito sequencial depende, em qualquer instante, além do valor actual das entradas, da sequência de valores que no passado foi aplicada nas entradas. Um circuito sequencial possui memória dos eventos passados.

#### 1.6. Ferramentas de CAD

O projecto de sistemas digitais não tem que recorrer obrigatoriamente a ferramentas de *software*. Contudo, as ferramentas de *software* são essenciais ao projecto de sistemas digitais. A utilização de HDLs (<u>Hardware Description Languages</u>), e das correspondentes ferramentas de simulação e síntese, está generalizada. Num ambiente CAD (*Computer-Aided Design*), as ferramentas melhoram a produtividade, ajudam a corrigir erros e a antever o comportamento. Algumas das tarefas que podem ser realizadas com a ajuda das ferramentas CAD são:

- Edição de esquemáticos;

- Compilação, simulação e síntese com HDLs;

- Análise da evolução dos sistemas ao longo do tempo;

- Simulação;

- Geração de vectores de teste.

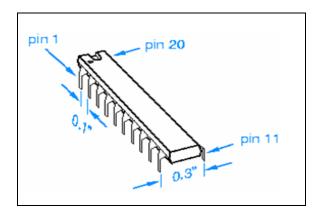

#### 1.7. Circuitos integrados

Um <u>circuito integrado</u> (CI) é uma colecção de portas lógicas produzidas num único *chip*. Os CIs podem ser classificados, de acordo com o seu tamanho, em:

- SSI (small scale integration): de 1 a 20 portas lógicas ANDs, Ors e NOTs;

- **MSI** (*medium scale integration*): 20 a 200 portas lógicas descodificadores, registos e contadores;

- **LSI** (*large scale integration*): 200 a 200.000 portas lógicas memórias de capacidade reduzida e PLDs simples;

- VLSI (very large scale integration): mais de 1 milhão de transístores microprocessadores, memórias e PLDs complexas.

Como exemplo, pode dizer-se que o Pentium4 tem 42 milhões de transístores.

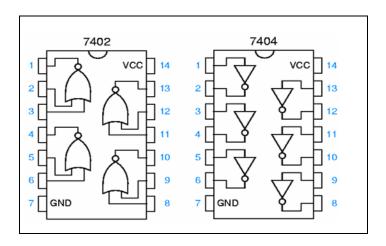

A figura seguinte mostra um exemplo de encapsulamento do tipo DIP (**D**ual **I**n-line **P**in package).

O <u>diagrama de pinos</u> da figura seguinte mostra a correspondência entre os sinais do dispositivo e os pinos do encapsulamento. Actualmente, os CIs do tipo SSI são usados como "cola" para formar componentes maiores em sistemas complexos. Os CIs do tipo SSI têm vindo a ser substituídos de forma generalizada por dispositivos de lógica programável (PLDs).

#### 1.8. PLDs

Alguns CIs permitem que a sua funcionalidade lógica seja programada no próprio *chip* após terem sido fabricados. A maior parte destes CIs pode mesmo ser **re**programada, o que permite que alguns erros sejam corrigidos sem ter que o substituir ou retirar. As **PLDs**: possuem uma estrutura a dois-níveis, com portas AND e OR, e ligações programáveis pelo utilizador. As **CPLDs** (PLDs complexas) e as **FPGAs** (*Field Programmable Gate Arrays*) foram idealizadas com o intuito de implementarem sistemas de maior dimensão. A utilização de **HDLs** e das respectivas **ferramentas** permite que um projecto seja compilado, sintetizado e descarregado para o dispositivo em menos tempo.

#### 1.9. Níveis de abstracção no projecto de sistemas digitais

O projecto de sistemas digitais pode decorrer em vários níveis de representação e de abstracção. Embora se possa ganhar experiência a projectar em determinado nível, por vezes é preciso mudar (subir e descer) de nível para concluir com sucesso certos projectos. O nível mais baixo é o da física do dispositivo e dos processos de fabrico do CI. Este nível não é leccionado em SD1. O nível seguinte é o do transístor. Este nível também não é leccionado em SD1.

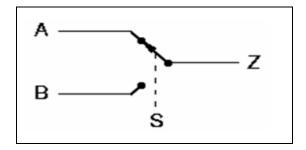

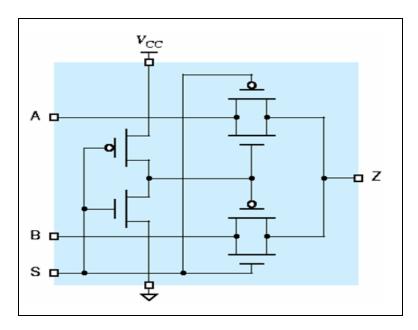

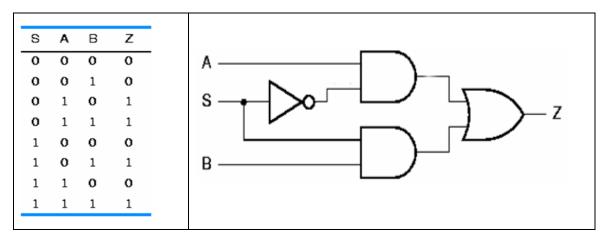

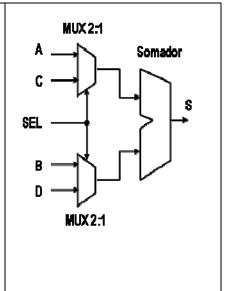

Para explicar o nível do transístor e os níveis seguintes, vamos usar um multiplexador com 2 bits de entrada (A e B), 1 bit de controlo (S) e 1 bit de saída (Z).

Para optimizar certas funções (ou módulos funcionais) é necessário projectá-las no <u>nível do transístor</u>. O multiplexador pode ser projectado em tecnologia CMOS, usando blocos estruturais à base de transístores. Utilizando esta abordagem, o multiplexador pode ser construído com 6 transístores apenas.

Segundo a forma tradicional de projectar um sistema, utiliza-se uma tabela de verdade para descrever a funcionalidade do multiplexador. Uma **tabela de verdade** contém todas as possíveis combinações dos valores de entradas e dos correspondentes valores das saídas. A partir da tabela de verdade, pode obter-se uma expressão minimizada para a saída do multiplexador: **Z = S'.A + S.B** Esta expressão pode ser convertida num diagrama no <u>nível da porta lógica</u>.

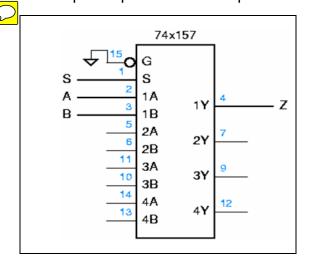

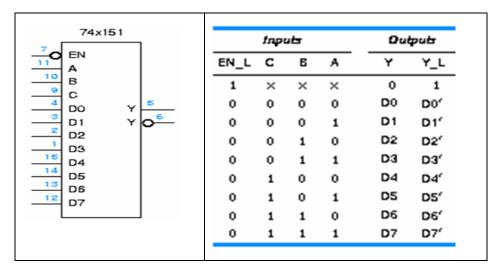

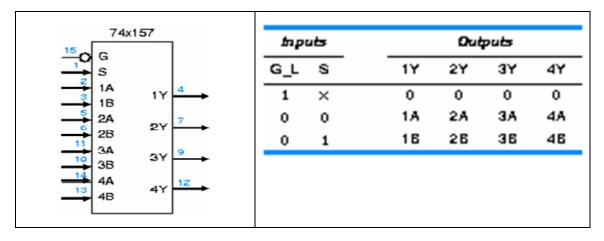

Para as funções mais frequentes, a maioria das tecnologias digitais dispõe de blocos elementares predefinidos. O 74x157 da figura seguinte é um CI do tipo MSI que faz a multiplexagem de 2 entradas de 4-bits. A figura mostra o diagrama do CI 74x157, no nível do bloco. Os números em azul identificam os pinos num encapsulamento DIP de 16-pinos que contém o dispositivo.

Também se pode usar HDLs, como o VHDL, para descrever a funcionalidade do multiplexador no <u>nível algorítmico</u> (ver figura seguinte). A declaração *entity* especifica quais as entradas e saídas do circuito. A declaração *architecture* define o comportamento do multiplexador. Uma ferramenta de síntese pode processar esta descrição algorítmica e gerar um circuito numa determinada tecnologia.

```

library IEEE;

use IEEE.std_logic_1164.all;

entity Vchaplmux is

port ( A, B, S: in STD_LOGIC;

Z: out STD_LOGIC );

end Vchaplmux;

architecture Vchaplmux_arch of Vchaplmux is begin

Z <= A when S = '0' else B;

end Vchaplmux_arch;</pre>

```

#### 2. Álgebra de Boole

O <u>sucesso</u> da tecnologia dos computadores baseia-se em 1º lugar na <u>simplicidade</u> com que se projectam circuitos digitais e na <u>facilidade</u> da sua produção. Os circuitos digitais são constituídos por unidades de processamento elementares, designadas por **portas lógicas**, e unidades de memória elementares, designadas por **flip-flops**. A simplicidade do projecto de circuitos digitais deve-se ao facto de as entradas e as saídas de cada porta lógica ou flip-flop assumir apenas 2 valores: 0 e 1. As alterações no valor dos sinais são determinadas pelas leis da **álgebra de Boole**. A álgebra de Boole permite **optimizar** funções. No projecto de circuitos digitais pode usar-se **técnicas de optimização de outras áreas**.

#### 2.1. Sinais binários

A lógica digital esconde a realidade analógica, ao mapear uma gama infinita de valores reais em apenas 2 valores: 0 e 1. A um valor lógico, 0 ou 1, é comum chamar-se um dígito binário (bit). Com n bits, pode representar-se 2n entidades distintas. Quando um projectista lida com circuitos electrónicos, é comum usar os termos "BAIXO" e "ALTO", em vez de "0" e "1". Considerar que 0 é BAIXO e 1 é ALTO, corresponde a usar lógica positiva. A correspondência oposta a esta é designada de lógica negativa.

|                                                        | State Rep                | preeenting Bit              |

|--------------------------------------------------------|--------------------------|-----------------------------|

| Technology                                             | 0                        | 1                           |

| Pneumatic logic                                        | Fluid at low pressure    | Fluid at high pressure      |

| Relay logic                                            | ⊂ircuit open             | Circuit closed              |

| Complementary metal-oxide<br>semiconductor(CMOS) logic | 0-1.5 V                  | 3.5-5.0 V                   |

| Transistor-transistor logic (TTL)                      | 0-0.8 V                  | 2.0-5.0 V                   |

| Fiber optics                                           | Lightoff                 | Lighton                     |

| Dynamic memory                                         | Capacitor discharged     | Capacitor charged           |

| Nonvolatile, erasable memory                           | Electrons trapped        | Electrons released          |

| Bipolar read-only memory                               | Fuse blown               | Fuse intact                 |

| Bubble memory                                          | No magnetic bubble       | Bubble present              |

| Magnetic tape or disk                                  | Flux direction "north"   | Flux direction "south"      |

| Pol ymer memo ry                                       | Molecule in state A      | Molecule in state B         |

| Read-only compact disc                                 | No pit                   | Pit                         |

| Rewriteable compact disc                               | Dye in crystalline state | Dye in noncrystalline state |

#### 2.2. Sistemas combinacionais vs. sequenciais

Um sistema lógico **combinacional** é aquele em que as saídas dependem apenas do valor actual das entradas. Um sistema combinacional pode ser descrito por uma **tabela de verdade**.

Além do valor actual das entradas, as saídas dum circuito lógico **sequencial** dependem também da sequência de valores por que passaram as entradas  $\Rightarrow$  memória. Um sistema sequencial pode ser descrito através duma **tabela de estados**.

Um sistema combinacional pode conter qualquer número de portas lógicas mas não ciclos de realimentação (feedback loops). Um ciclo de realimentação é um caminho dum circuito, que permite a um sinal de saída duma porta ser propagado de volta para a entrada dessa porta.

Regra geral, os ciclos de realimentação introduzem um comportamento sequencial nos circuitos.

#### 2.3. Portas lógicas

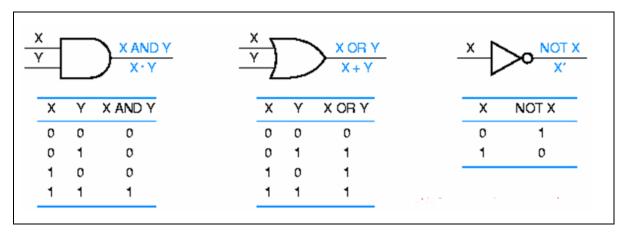

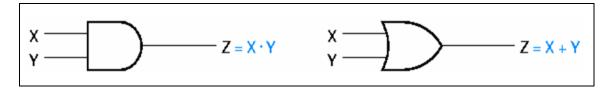

Com 3 tipos de porta elementares (AND, OR, NOT) consegue construir-se qualquer sistema digital combinacional, ou seja, formam um **conjunto completo**.

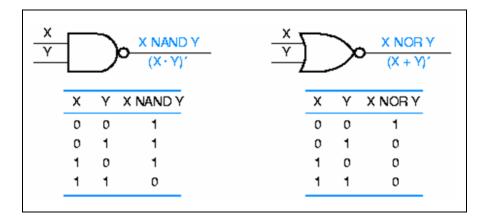

Os símbolos e as tabelas de verdade do AND e do OR podem ser generalizados para portas com qualquer número de entradas. A <u>bolha</u> na saída do inversor representa um comportamento "invertido". Combinando numa única porta, um NOT com uma função AND ou OR, obtêm-se 2 novas funções lógicas: NAND e NOR.

O símbolo e a tabela de verdade do NAND e do NOR também podem ser generalizados para portas com qualquer número de entradas.

#### 2.4. Álgebra da comutação (switching)

Em 1854, G. Boole [1815-1865] introduziu o formalismo que ainda usamos para tratar a lógica de forma sistemática, a **álgebra de Boole**.

Em 1938, C. Shannon [1916-2001] utilizou esta álgebra para provar que as propriedades dos circuitos de comutação eléctricos podem ser representados por uma álgebra de Boole com 2-valores, a **álgebra da comutação**.

Usando esta álgebra, pode equacionar-se proposições (afirmações) que serão verdadeiras ou falsas. Combinando-as, geram-se novas proposições e pode concluir-se se elas são verdadeiras ou falsas. Shannon usava uma variável simbólica (por ex. X) para representar a condição associada a um sinal lógico, em que ele assumia um de 2 valores possíveis ("0" ou "1").

#### 2.5. Axiomas

Os **axiomas** (ou postulados) dum sistema matemático são um conjunto mínimo de definições elementares, que se considera serem verdadeiras. O 1º par de axiomas incorpora a **abstracção digital** (X só pode assumir 2 valores):

**(A1)** X=0 se X

$$\neq$$

1 (A1') X=1 se X $\neq$ 0

Este par de axiomas apenas difere na permuta dos símbolos 0 e 1. Este princípio aplica-se a todos os axiomas e está na origem da **dualidade**. O próximo par de axiomas incorpora a notação de função **inversor**:

em que a plica (') denota a função inversor.

Os últimos 3 pares de axiomas enunciam a definição formal das operações **AND** (multiplicação lógica) e **OR** (adição lógica):

**(A3)**

$$0.0 = 0$$

(A3')  $1+1 = 1$

**(A4)**  $1.1 = 1$  (A4')  $0+0 = 0$

**(A5)**  $0.1 = 1.0 = 0$  (A5')  $1+0 = 0+1 = 1$

Por convenção, numa expressão lógica contendo multiplicação e adição, a multiplicação tem **precedência**. A expressão X·Y+Y·Z' é equivalente a (X·Y)+(Y·Z'). Os axiomas A1-A5 e A1'-A5' definem de forma completa a **álgebra Boole**.

#### 2.6. Teoremas

Os **teoremas** são declarações, que se sabe serem verdadeiras, que permitem manipular expressões algébricas de modo a que a análise seja mais simples e/ou a síntese dos circuitos correspondentes seja mais eficiente.

Apresentam-se a seguir os teoremas envolvendo apenas **uma** variável:

(T1)

$$X+0 = X$$

(T1')  $X\cdot 1 = X$

(Identidades)

(T2)  $X+1 = 1$

(T2')  $X\cdot 0 = 0$

(Elementos nulos)

(T3)  $X+X = X$

(T3')  $X\cdot X = X$

(Idempotência)

(T4)  $(X')' = X$

(Involução)

(T5)  $X+X' = 1$

(T5')  $X\cdot X' = 0$

(Complementos)

Pode provar-se que estes teoremas são verdadeiros. Segue-se a prova de T1:

```

[X=0] 0+0=0 (verdade, segundo A4')

[X=1] 1+0=1 (verdade, segundo A5')

```

Os teoremas envolvendo 2 ou 3 variáveis são:

```

X+Y=Y+X

X \cdot Y = Y \cdot X

(Comutatividade)

(T6)

(T6')

(X+Y)+Z = X+(Y+Z)

(T7')

(X \cdot Y) \cdot Z = X \cdot (Y \cdot Z)

(Associatividade)

X \cdot Y + X \cdot Z = X \cdot (Y + Z)

(X+Y)\cdot(X+Z)=X+Y\cdot Z

(Distributividade)

(8T)

(T8')

X+X\cdot Y=X

X \cdot (X+Y) = X

(T9)

(T9')

(Cobertura)

(T10) X \cdot Y + X \cdot Y' = X

(T10') (X+Y)\cdot(X+Y') = X

(Combinação)

(T11) X \cdot Y + X' \cdot Z + Y \cdot Z = X \cdot Y + X' \cdot Z

(Consenso)

(T11') (X+Y)\cdot(X'+Z)\cdot(Y+Z) = (X+Y)\cdot(X'+Z)

```

Convém ter em tenção que o teorema T8' não é verdadeiro com inteiros ou reais. Os teoremas T9 e T10 são usados para **minimizar** funções lógicas.

Vários teoremas importantes são verdadeiros para um nº arbitrário de variáveis. Daqui resultam teoremas envolvendo *n* variáveis:

Teoremas da idempotência generalizada:

(T12)

$$X+X+...+X=X$$

(T12')  $X\cdot X\cdot ...\cdot X=X$

Teoremas de DeMorgan:

(T13)

$$(X1 \cdot X2 \cdot ... \cdot Xn)' = X1' + X2' + ... + Xn'$$

(T13')  $(X1 + X2 + ... + Xn)' = X1' \cdot X2' \cdot ... \cdot Xn'$

Teorema de DeMorgan generalizado:

(T14)

$$[F(X1,X2,...,Xn,0,1,+,\cdot)]' = F(X1',X2',...,Xn',1,0\cdot,+)$$

Teoremas da expansão de Shannon:

(T15)

$$F(X1,X2,...,Xn) = X1 \cdot F(1,X2,...,Xn) + X1' \cdot F(0,X2,...,Xn)$$

(T15')  $F(X1,X2,...,Xn) = [X1+F(0,X2,...,Xn)] \cdot [X1'+F(1,X2,...,Xn)]$

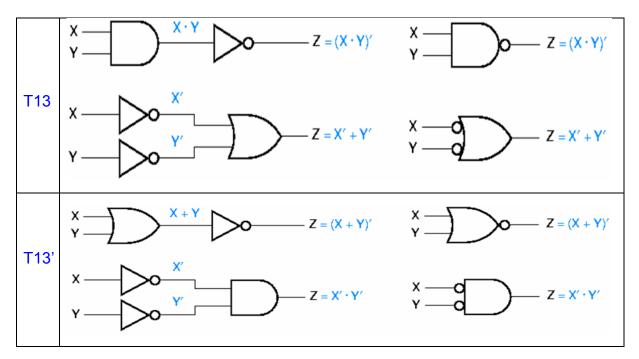

Os teorema de DeMorgan (T13 e T13') para 2 varáveis (n=2) ficam:

$$(X \cdot Y)' = X' + Y'$$

$(X+Y)' = X' \cdot Y'$

Augustus De Morgan [1806-1871]

O Teorema de DeMorgan estabelece um procedimento para **complementar funções** lógicas. Pode usar-se o teorema de DeMorgan para converter expressões AND-OR em expressões OR-AND, como se mostra no próximo exemplo.

#### Exemplo:

```

Z = A' B' C + A' B C + A B' C + A B C' (expressão AND-OR)

Z' = (A + B + C') \cdot (A + B' + C') \cdot (A' + B + C') \cdot (A' + B' + C) (expressão OR-AND)

```

Também se podem usar os teoremas de DeMorgan para saber a equivalência entre portas lógicas:

Como a álgebra de Boole só possui 2 valores, também se pode demonstrar a validade dos teoremas através de **tabelas de verdade**. Para isso, constrói-se uma tabela de verdade para cada lado das equações presentes num teorema. O exemplo seguinte prova a veracidade dos teoremas de DeMorgan [T13 e T13'] para n=2:

| (X+Y)' = X'·Y' | X<br>0<br>0<br>1 | Y<br>0<br>1<br>0      | T<br>1<br>1<br>0 | 7<br>1<br>0<br>1<br>0 | 1<br>0<br>0<br>0              | 7Y<br>1<br>0<br>0<br>0  |

|----------------|------------------|-----------------------|------------------|-----------------------|-------------------------------|-------------------------|

| (X·Y)' = X'+Y' | X<br>0<br>0<br>1 | Y<br>0<br>1<br>0<br>1 | 1<br>1<br>0<br>0 | 1<br>0<br>1<br>0      | 7. Y<br>1<br>1<br>1<br>1<br>0 | X+Y<br>1<br>1<br>1<br>0 |

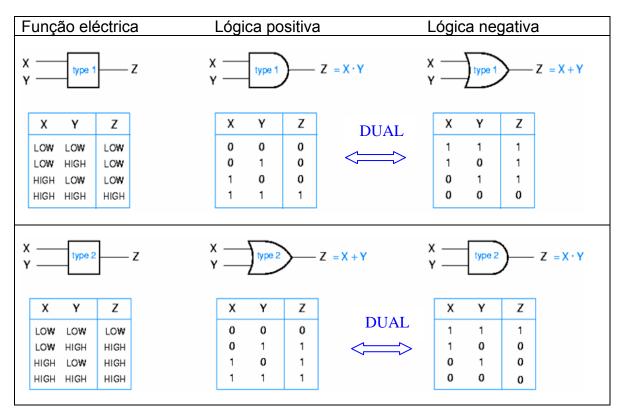

#### 2.7. Dualidade

Os teoremas anteriores foram apresentados aos pares. A versão primária dum teorema pode ser obtida da versão secundária trocando "0" com "1" e "·" com "+".

<u>Princípio da dualidade</u>: qualquer teorema ou identidade da Álgebra de Boole continua a ser verdadeiro quando se trocam todos os "0" com "1" e todos os "·" com "+".

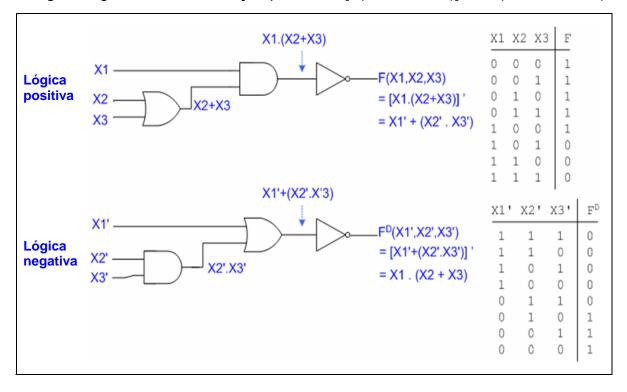

A dualidade é importante porque duplica a utilidade de qualquer axioma/teorema da Álgebra de Boole e da manipulação de funções lógicas. Verifica-se que o dual duma expressão lógica é a mesma expressão em que "+" e ":" foram trocados:

$$F^{D}(X_{1},X_{2},...,X_{n},0,1,+,\cdot,') = F(X_{1},X_{2},...,X_{n},1,0,\cdot,+,').$$

Não se deve confundir a dualidade com os teoremas de DeMorgan:

$$\begin{array}{lll} [F(X_1, X_2, ..., X_n, +, \cdot)]' & = & F(X_1', X_2', ..., X_n', \cdot, +) \\ [F(X_1, X_2, ..., X_n, +, \cdot)]' & = & F^D(X_1', X_2', ..., X_n', +, \cdot) \end{array}$$

A figura seguinte ilustra a aplicação prática da expressão do dual.

A figura seguinte é uma ilustração prática de [F(X1,X2,...,Xn)]' = F<sup>D</sup>(X1',X2',...,Xn').

#### 2.8. Representação normalizada

A representação mais elementar duma função lógica é a tabela de verdade. A **tabela de verdade** indica qual é a saída do circuito para cada combinação de entradas possível. A tabela de verdade duma função de **n**-variáveis possui **2**<sup>n</sup> linhas.

| OW. | Х | Υ | Z | F        | Row | Х | Υ | Z |   |

|-----|---|---|---|----------|-----|---|---|---|---|

|     | 0 | 0 | 0 | F(0,0,0) | 0   | 0 | 0 | 0 |   |

| 1   | 0 | 0 | 1 | F(0,0,1) | 1   | 0 | 0 | 1 | ( |

| 2   | 0 | 1 | 0 | F(0,1,0) | 2   | 0 | 1 | 0 | ( |

| 3   | 0 | 1 | 1 | F(0,1,1) | 3   | 0 | 1 | 1 | 1 |

| 4   | 1 | 0 | 0 | F(1,0,0) | 4   | 1 | 0 | 0 | 1 |

| 5   | 1 | 0 | 1 | F(1,0,1) | 5   | 1 | 0 | 1 | C |

| 6   | 1 | 1 | 0 | F(1,1,0) | 6   | 1 | 1 | 0 | 1 |

| 7   | 1 | 1 | 1 | F(1,1,1) | 7   | 1 | 1 | 1 | 1 |

Existem  $2^8$  funções lógicas de 3 variáveis diferentes, em que o número de linhas é  $2^3 = 8$  e os valores possíveis por linha são  $\{0,1\} = 2$ .

Como as tabelas de verdade apenas são viáveis com poucas variáveis, é conveniente saber convertê-las para expressões algébricas. Apresentam-se agora algumas definições a usar com as expressões algébricas.

Um **literal** é uma variável ou o complemento duma variável. Exemplo: X, Y, X'.

Um **termo de produto** é um literal ou um produto lógico de 2 ou mais literais. Exemplo: Z', W·X·Y, W·X·Y'

A **soma-de-produtos** (**SOP**) é uma soma lógica de termos de produto. Exemplo: Z' + W·X·Y

Um **termo de soma** é um literal ou uma soma lógica de 2 ou mais literais. Exemplo: Z', W+X+Y, W+X'+Y'

O **produto-de-somas** (**POS**) é um produto lógico de termos de soma. Exemplo: Z' · (W+X+Y)

Um **termo normal** é um termo de produto, ou de soma, em que cada variável só aparece uma vez. Exemplos de termos **não**-normais: W·X·X·Z', W'+Y'+Z+W'

Um **mintermo** de n-variáveis é um termo de produto normal com **n** literais. Exemplos com 4 variáveis: W·X·Y·Z', W·X·Y·Z

Um **maxtermo** de n-variáveis é um termo de soma normal com **n** literais. Exemplos com 4 variáveis: W+X+Y+Z', W'+X'+Y+Z

Há uma correspondência entre a tabela de verdade e os mintermos e maxtermos. Um mintermo é um termo de produto que é 1 numa linha da tabela de verdade, enquanto um maxtermo é um termo de soma que é 0 numa linha da tabela de verdade.

A tabela que se segue mostra, a título de exemplo, os mintermos e maxtermos para uma função de 3-variáveis F(X,Y,Z).

| Row | Х | Υ | Z | F         | Mintern               | Maxterm    |

|-----|---|---|---|-----------|-----------------------|------------|

| 0   | 0 | 0 | 0 | F(0,0,0)  | X'-Y'-Z'              | X + Y + Z  |

| 1   | 0 | 0 | 1 | F(0,0,1)  | X'-Y'-Z               | X + Y + Z' |

| 2   | 0 | 1 | 0 | F(0, 1,0) | $X' \cdot Y \cdot Z'$ | X + Y' + Z |

| 3   | 0 | 1 | 1 | F(0,1,1)  | $X' \cdot Y \cdot Z$  | X + Y'+ Z' |

| 4   | 1 | 0 | 0 | F(1,0,0)  | X - Y' - Z'           | X'+Y+Z     |

| 5   | 1 | 0 | 1 | F(1,0,1)  | X - Y' - Z            | X'+ Y + Z' |

| 6   | 1 | 1 | 0 | F(1,1,0)  | $X \cdot Y \cdot Z'$  | X'+ Y'+ Z  |

| 7   | 1 | 1 | 1 | F(1,1,1)  | $X \cdot Y \cdot Z$   | X'+Y'+Z'   |

Um mintermo de **n**-variáveis pode ser representado por um inteiro com **n**-bits, que se designa por <u>número</u> do <u>mintermo</u>. No mintermo **i**, uma variável surge complementada se o bit correspondente na representação binária de **i** for 0; senão, a variável é não-complementada. Por exemplo, à linha 5 (101) corresponde o mintermo X·Y·Z. No maxtermo **i**, uma variável surge complementada se o bit correspondente na representação binária de **i** for 1; senão, a variável é não-complementada. Por exemplo, à linha 5 (101) corresponde o maxtermo X'+Y+Z'. Para que a especificação dos mintermos e maxtermos faça sentido, é preciso conhecer o número de variáveis da função e a sua ordem (X,Y,Z nos exemplos).

A partir da correspondência entre a tabela de verdade e os <u>mintermos</u>, pode derivar-se uma representação algébrica dessa função lógica. A **soma canónica** duma função lógica é uma soma dos mintermos que correspondem a linhas da tabela de verdade para as quais a função é 1. Por exemplo, a partir da tabela seguinte obtém-se:

$$F = \sum_{X,Y,Z} m(0,3,4,6,7) = X' \cdot Y' \cdot Z' + X' \cdot Y \cdot Z + X \cdot Y' \cdot Z' + X \cdot Y \cdot Z' + X \cdot Y \cdot Z'$$

A notação  $\sum_{X,Y,Z} m(0,3,4,6,7)$  identifica 1 <u>lista de mintermos</u> e representa a soma dos mintermos 0, 3, 4, 6 e 7 envolvendo as variáveis X, Y e Z.

À lista de mintermos também se pode dar o nome de on-set da função lógica.

| Row | Х | Υ | Z | F |

|-----|---|---|---|---|

| 0   | 0 | 0 | 0 | 1 |

| 1   | 0 | 0 | 1 | 0 |

| 2   | 0 | 1 | 0 | 0 |

| 3   | 0 | 1 | 1 | 1 |

| 4   | 1 | 0 | 0 | 1 |

| 5   | 1 | 0 | 1 | 0 |

| 6   | 1 | 1 | 0 | 1 |

| 7   | 1 | ı | 1 | 1 |

A partir da correspondência entre a tabela de verdade e os <u>maxtermos</u>, pode derivar-se uma representação algébrica dessa função lógica. O **produto canónico** duma função lógica é um produto dos maxtermos que correspondem a linhas da tabela de verdade para as quais a função é 0.

| Row | Х | Υ | Z | F |

|-----|---|---|---|---|

| 0   | 0 | 0 | 0 | 1 |

| 1   | 0 | 0 | 1 | 0 |

| 2   | 0 | 1 | 0 | 0 |

| 3   | 0 | 1 | 1 | 1 |

| 4   | 1 | 0 | 0 | 1 |

| 5   | 1 | 0 | 1 | 0 |

| 6   | 1 | 1 | 0 | 1 |

| 7   | 1 | 1 | 1 | 1 |

Como exemplo, a partir da próxima tabela obtém-se:

$$F = \prod_{X,Y,Z} M(1,2,5) = (X+Y+Z') \cdot (X+Y'+Z) \cdot (X'+Y+Z')$$

A notação  $\prod_{X,Y,Z} M(1,2,5)$  identifica uma <u>lista de maxtermos</u> e representa o produto dos maxtermos 1, 2 e 5 envolvendo as variáveis X, Y e Z.

À lista de maxtermos também se pode dar o nome de **off-set** da função lógica. É fácil converter uma lista de mintermos numa lista de maxtermos. Para uma função de **n**-variáveis, os mintermos e maxtermos pertencem ao conjunto {0, 1, ..., 2<sup>n</sup>-1}. Uma lista de mintermos ou de maxtermos é um subconjunto destes números. Para mudar dum tipo de lista para o outro, utiliza-se o subconjunto de números complementar.

Alguns exemplos:

Foram apresentadas 5 formas distintas de representar funções lógicas combinacionais:

- A tabela de verdade

- A soma algébrica de mintermos (a soma canónica)

- A lista de mintermos, com notação ∑

- Produto algébrico de maxtermos (o produto canónico)

- A lista de maxtermos, com notação ∏

Qualquer destas representações contém exactamente a mesma informação. A partir duma delas, pode derivar-se cada uma das outras 4 aplicando uma regra de conversão simples.

#### 2.9. Exemplos

1. Para  $F = X \cdot Y + X \cdot Y \cdot Z + X' \cdot Y \cdot Z$ , obter a expressão de F' na forma produto de somas.

```

F' = (X.Y + X.Y'.Z + X'.Y.Z)'

= (X.Y)' \cdot (X.Y'.Z)' \cdot (X'.Y.Z)'

= (X'+Y') \cdot (X'+Y+Z') \cdot (X+Y'+Z')

```

**2.** Escreva a função  $G(X,Y,Z) = X + Y \cdot Z$  como uma lista de mintermos

```

G = X + Y \cdot Z

= X \cdot (Y+Y') \cdot (Z+Z') + Y \cdot Z \cdot (X+X') [T5]

= XYZ + XYZ' + XY'Z + XY'Z' + XYZ + X'YZ

= X'YZ + XY'Z' + XY'Z + XYZ' + XYZ [T3]

= \sum_{x,y,z} m(3,4,5,6,7)

```

3. Obter o produto de maxtermos para a função H = X'·Y' + X·Z.

Em cada soma da expressão anterior falta uma variável:

```

X+Y' = X+Y'+ZZ' = (X+Y'+Z)(X+Y'+Z') [T5'] [T8']

X'+Z = X'+Z+YY' = (X'+Y+Z)(X'+Y'+Z) [T5'] [T8']

Y'+Z = Y'+Z+XX' = (X+Y'+Z)(X'+Y'+Z) [T5'] [T8']

```

Combinando estes termos:

```

H = (X+Y'+Z)(X+Y'+Z')(X'+Y+Z)(X'+Y'+Z)(X+Y'+Z)(X'+Y'+Z)

= \prod_{X,Y,Z} M(2,3,4,6)

```

**4**. Obter a lista de maxtermos para  $H = X' \cdot Y' + X \cdot Z$ , usando a tabela de verdade que se segue.

| Χ | Υ | <b>Z</b> | W |

|---|---|----------|---|

| 0 | 0 | 0        | 1 |

| 0 | 0 | 1        | 1 |

| 0 | 1 | 0        | 0 |

| 0 | 1 | 1        | 0 |

| 1 | 0 | 0        | 0 |

| 1 | 0 | 1        | 1 |

| 1 | 1 | 0        | 0 |

| 1 | 1 | 1        | 1 |

A partir da tabela obtém-se:

$$H = \prod_{x,y,z} M(2,3,4,6)$$

$$H = \sum_{x,y,z} m(0,1,5,7)$$

Compare esta solução com a que se obteve no exemplo 3.

**5.** Obter uma expressão para J = XYZ + XYZ' + XY'Z + X'YZ com um número reduzido de operadores.

```

J = XYZ + XYZ' + XYZ + XY'Z + XYZ + X'YZ [T3] X+X=X

= XY(Z+Z') + X(Y+Y')Z + (X+X')YZ

= XY+XZ+YZ [T5] X+X'=1

```

#### 3. Conceitos sobre Sistemas Combinacionais

#### 3.1. Análise, síntese e alterações a um circuito

Após obter a descrição formal da função lógica dum circuito, pode (i) determinar-se o seu comportamento para várias combinações de entradas; (ii) alterar-se a descrição algébrica de modo a induzir diferentes estruturas para o circuito; (iii) transformar a descrição algébrica numa forma normalizada (por exemplo, PLD); (iv) utilizar a descrição algébrica do circuito para analisar um sistema de maior dimensão, do qual este sistema seja parte integrante.

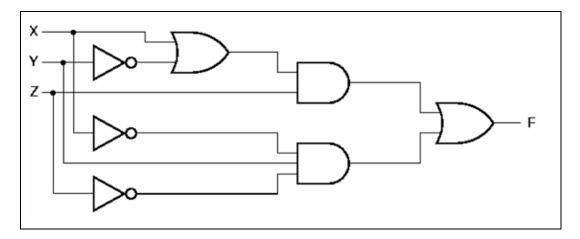

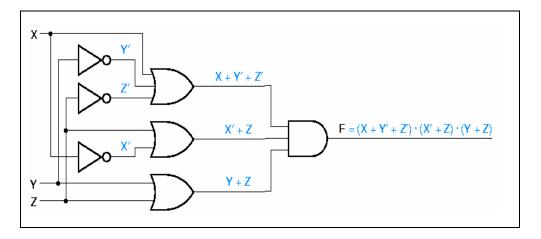

Considere-se o seguinte circuito.

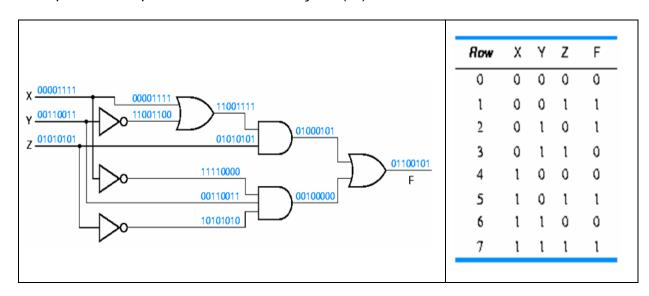

Pode obter-se a <u>tabela de verdade</u> do circuito inspeccionando o seu comportamento para todas as combinações (2<sup>n</sup>) das entradas.

A partir da tabela de verdade pode extrair-se de forma directa uma expressão lógica (por exemplo, SOP).

Esta técnica é muito morosa e só é exequível se o número de variáveis de entrada for reduzido. A solução é recorrer à <u>abordagem algébrica</u>.

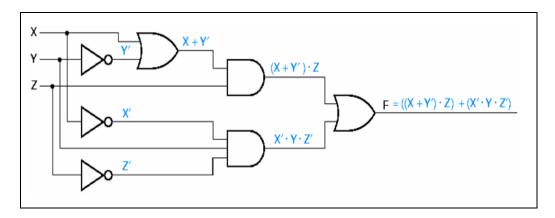

<u>Abordagem algébrica:</u> é uma abordagem em que se analisa o circuito desde as entradas até às saídas, construindo uma expressão correspondente aos operadores e à estrutura do circuito

Aplicando a abordagem algébrica ao circuito anterior obtém-se:  $F = ((X+Y') \cdot Z) + (X' \cdot Y \cdot Z')$

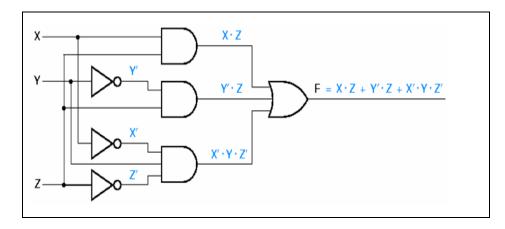

Após aplicar uma transformação algébrica obtém-se uma expressão e um circuito diferentes

$$F = ((X+Y') \cdot Z) + (X' \cdot Y \cdot Z')$$

$$= (X \cdot Z) + (Y' \cdot Z) + (X' \cdot Y \cdot Z')$$

A partir da expressão de F original, também se pode derivar uma expressão do tipo POS (aplicando T8' e T5):

$$F = ((X+Y') \cdot Z) + (X' \cdot Y \cdot Z')$$

$$= (X+Y'+X') \cdot (X+Y'+Y) \cdot (X+Y'+Z') \cdot (Z+X') \cdot (Z+Y) \cdot (Z+Z')$$

$$= 1 \cdot 1 \cdot (X+Y'+Z') \cdot (Z+X') \cdot (Z+Y) \cdot 1 = [T5]$$

$$= (X+Y'+Z') \cdot (X'+Z) \cdot (Y+Z)$$

O ponto de partida para projectar um circuito combinacional é normalmente a sua descrição em linguagem natural (por exemplo, em português).

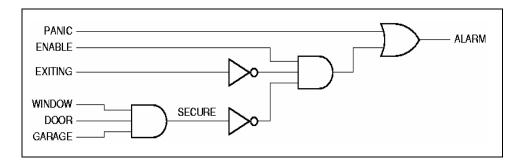

#### **Exemplo**: construir um circuito de alarme.

"A saída ALARM é 1 se a entrada PANIC for 1 **ou** se a entrada ENABLE for 1, a entrada EXITING for 0 e a casa não estiver segura. A casa é segura se as entradas WINDOW, DOOR e GARAGE forem todas 1".

ALARM = PANIC + ENABLE • EXITING · SECURE SECURE = WINDOW • DOOR • GARAGE

O circuito que concretiza a expressão de ALARM é o que se apresenta abaixo.

A concretização da expressão de ALARM na forma SOP é:

```

ALARM= PANIC + ENABLE • EXITING' • (WINDOW • DOOR • GARAGE)'

ALARM= PANIC + ENABLE • EXITING' • (WINDOW' + DOOR' + GARAGE')

ALARM= PANIC + ENABLE • EXITING' • WINDOW' +

ENABLE • EXITING' • DOOR' + ENABLE • EXITING' • GARAGE'

```

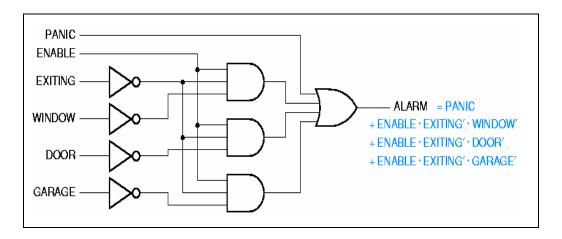

à qual corresponde o seguinte circuito:

Outras vezes, a descrição começa com uma listagem das combinações das entradas para as quais uma determinada saída deve estar <u>activa</u> ou <u>inactiva</u>. Esta listagem equivale à tabela de verdade dessa saída.

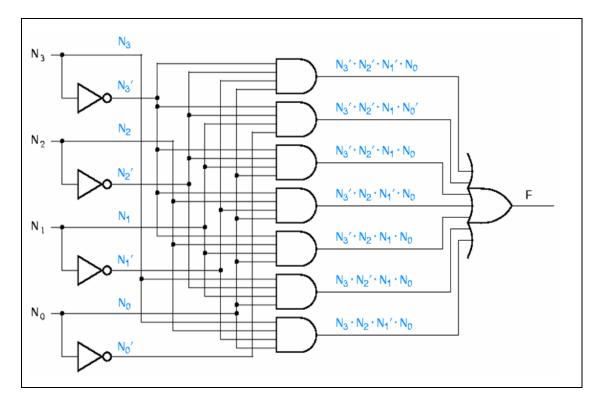

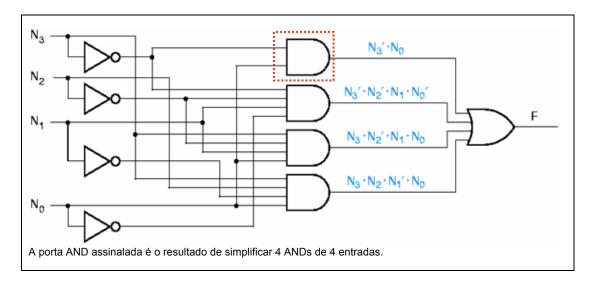

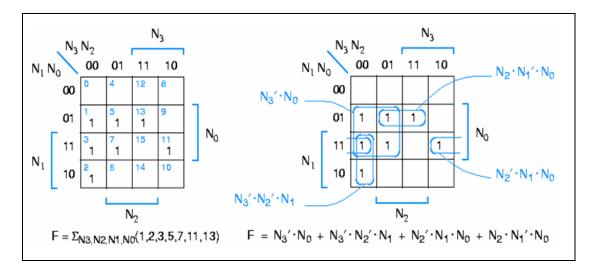

**Exemplo**: construir um circuito que detecte números primos de 4-bits. "Dada uma combinação de entrada N=N<sub>3</sub>N<sub>2</sub>N<sub>1</sub>N<sub>0</sub> com 4-bits, o circuito gera 1 na saída quando N=1,2,3,5,7,11,13 e gera 0 nos outros casos."

$$\begin{array}{lll} F & = & \sum_{N3,N2,N1,N0} m(1,2,3,5,7,11,13) = \\ & & N_3^{'} \cdot N_2^{'} \cdot N_1^{'} \cdot N_0 + N_3^{'} \cdot N_2^{'} \cdot N_1 \cdot N_0^{'} + N_3^{'} \cdot N_2^{'} \cdot N_1 \cdot N_0 + N_3^{'} \cdot N_2^{'} \cdot N_1^{'} \cdot N_0 + \\ & & N_3^{'} \cdot N_2^{'} \cdot N_1^{'} \cdot N_0 + N_3^{'} \cdot N_2^{'} \cdot N_1^{'} \cdot N_0 + N_3^{'} \cdot N_2^{'} \cdot N_1^{'} \cdot N_0 \end{array}$$

A concretização da expressão SOP da saída do detector é:

Até aqui foram apresentados métodos para projectar circuitos que usam apenas portas AND, OR e NOT. Em certas situações, o projectista pode querer usar portas NAND ou NOR, dado que são mais rápidas que AND's e OR's na maioria das tecnologias. Contudo, a generalidade das pessoas não desenvolve proposições lógicas usando o NAND e o NOR como elementos de ligação. Não se diz: "Não gosto duma rapariga, se ela não for inteligente ou não for elegante  $\bf e$  também se ela não for rica ou não for simpática", ou seja,  $\bf G'=(l'+E')\cdot(R'+S')$ . É mais frequente dizerse: "Gosto duma rapariga, se ela for inteligente e elegante  $\bf ou$  se ela for rica e simpática", ou seja,  $\bf G=(l\cdot E)+(R\cdot S)$ .

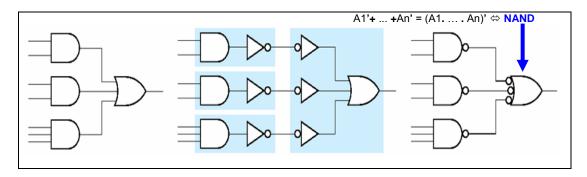

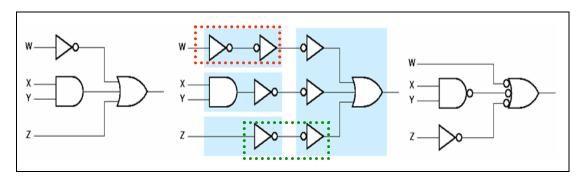

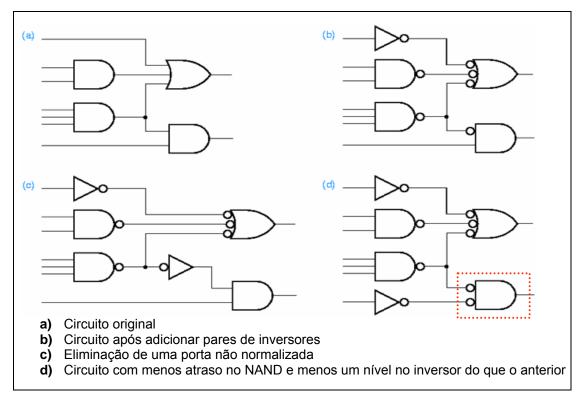

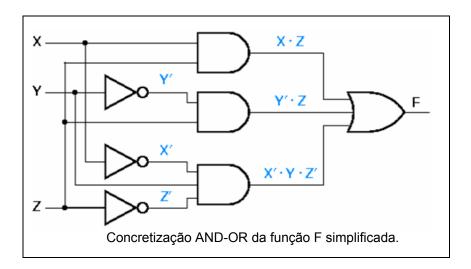

Qualquer expressão lógica pode ser convertida numa expressão SOP equivalente e ser deste modo implementada com portas AND e OR. Um circuito AND-OR com 2-níveis pode ser convertido num circuito NAND-NAND com 2-níveis, através duma simples substituição de portas (ver o exemplo abaixo).

Se os termos (de produto) da expressão SOP incluírem apenas um literal, os inversores a aplicar a esse termo podem ser ou não necessários (ver o exemplo abaixo).

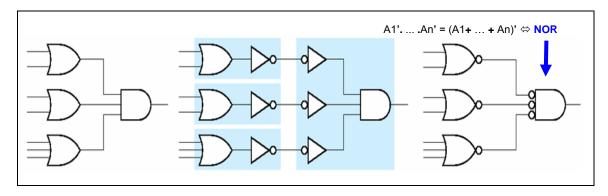

Vimos que qualquer expressão SOP pode ser concretizada de duas formas: através dum circuito AND-OR ou dum circuito NAND-NAND. Aplicando o princípio da dualidade a esta regra, obtemos uma declaração que também é verdadeira:

Qualquer expressão POS pode ser concretizada de duas formas: através dum circuito OR-AND ou dum circuito NOR-NOR.

A figura seguinte mostra a aplicação do princípio da dualidade.

Estas alterações, como por exemplo a conversão para a estrutura NAND-NAND, podem ser aplicadas a qualquer circuito lógico.

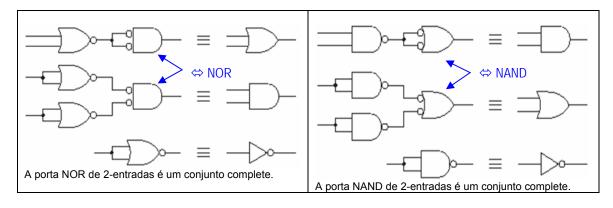

Qualquer conjunto de tipos de porta lógica que permite concretizar qualquer função lógica é um **conjunto completo**. A porta AND de 2-entradas mais a porta OR de 2-entradas mais o inversor formam 1 conjunto complete. A figura seguinte mostra outros conjuntos completos: (i) a porta NAND de 2-entradas e (ii) a porta NOR de 2-entradas.

Qualquer função lógica pode ser expressa numa soma de produtos de literais. As portas AND e OR, com qualquer número de entradas, podem ser construídas a partir de portas do mesmo tipo com 2-entradas.

#### 3.2. Minimização

Normalmente não é económico concretizar uma função lógica directamente a partir da 1ª expressão que ocorre. Isto porque as expressões canónicas (soma e produto) são especialmente consumidoras de recursos. A minimização de lógica emprega diversas técnicas para obter a implementação mais simples possível ao nível-daporta para uma função. Contudo, o grau de simplificação depende da métrica usada. Três exemplos de métricas que podem ser usadas são:

- Número de literais;

- Número de portas (lógicas);

- Número de níveis de portas em cascata.

O número de literais mede a quantidade de ligações necessária para implementar uma função. O número de portas mede a área (espaço ocupado) do circuito. Existe uma relação directa entre o número de portas dum projecto e o número de circuitos integrados necessário à sua implementação. O número de níveis de portas mede o número de portas entre as entradas e as saídas do circuito. Quanto maior é o número de níveis, maior é o atraso no circuito. Verifica-se que ao adequar um circuito para apresentar um atraso mínimo, raramente se consegue uma implementação com o menor número de portas ou com as portas mais simples possíveis. Não é possível minimizar as três métricas ao mesmo tempo. Apresentase a seguir um exemplo que ilustra várias alternativas de simplificação duma função.

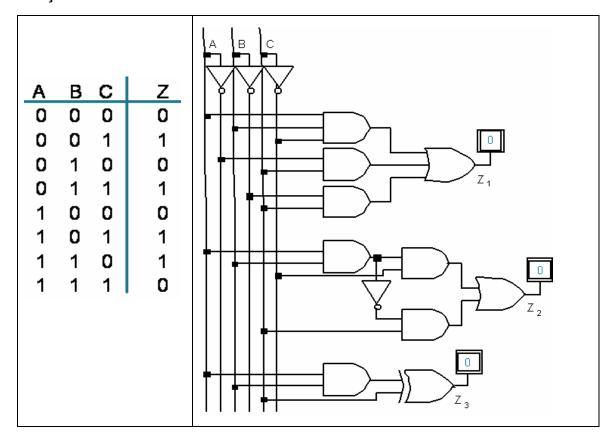

#### Dada a função

```

Z = A'B'C+A'BC+AB'C+ABC'=A'(B'+B)C+(A'+A)B'C+ABC'

= A'C+B'C+ABC'

```

- i) A implementação Z₁ na figura anterior constitui uma concretização a dois-níveis (dado que os inversores não contam), em que o número de literais é maior que nas outras alternativas.

- ii) A implementação  $Z_2$  é uma concretização multi-nível, que utilize portas com menos entradas mas possui um número de níveis maior:

```

Z = ABC'+A'C+B'C

= (AB)C'+(A'+B')C

= (AB)C'+(AB)'.C

```

iii) A implementação Z<sub>3</sub> é uma concretização que utilize uma porta mais complexa (XOR), que significa um atraso maior, mas emprega menos portas:

```

Z = (AB)C'+(AB)'.C = (AB) xor C

```

As técnicas de minimização reduzem o número e o tamanho das portas necessárias para construir um circuito, diminuindo assim o custo do sistema. Os métodos de minimização reduzem o custo dum circuito AND-OR ou OR-AND a 2-níveis através de:

- Minimizar o número de portas no primeiro nível;

- Minimizar o número de entradas em cada porta do primeiro nível;

- Minimizar o número de entradas em cada porta do segundo nível.

Os métodos de minimização não consideram o custo dos inversores à entrada. Isto resulta de se considerar que todas as variáveis de entrada, e seus complementares, estão disponíveis (adequado para implementações com PLD's). Também assumem que a função a minimizar está representada por uma tabela de verdade ou por uma lista de mintermos ou maxtermos. A minimização baseia-se nos teoremas **T10** e **T10**':

```

produto·Y + produto·Y' = produto

(soma + Z) · (soma + Z') = soma

```

Estes teoremas indicam que "se dois termos diferem apenas numa variável, podem ser substituídos por um único termo com menos uma variável". Deste modo, poupase uma porta e a outra porta possui menos uma entrada.

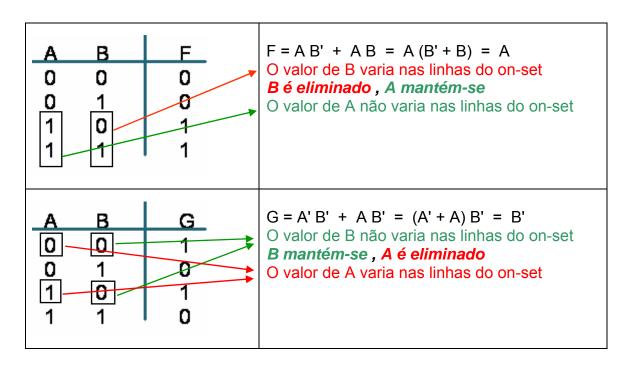

#### Essência da simplificação:

Encontrar pares de elementos do ON-set em que apenas uma variável muda de valor. A variável que muda de valor pode ser eliminada.

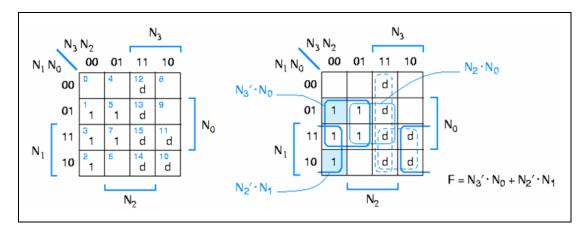

Vamos aplicar esta técnica à expressão do detector de números primos.

```

\begin{split} F &= \sum_{N_3,N_2,N_1,N_0} m(1,2,3,5,7,11,13) = \\ &\quad N_3' \cdot N_2' \cdot N_1' \cdot N_0 + \quad N_3' \cdot N_2' \cdot N_1 \cdot N_0 + \quad N_3' \cdot N_2 \cdot N_1' \cdot N_0 + \quad N_3' \cdot N_2 \cdot N_1 \cdot N_0 + \dots = \\ &\quad (N_3' \cdot N_2' \cdot N_1' \cdot N_0 + \quad N_3' \cdot N_2' \cdot N_1 \cdot N_0) + (N_3' \cdot N_2 \cdot N_1' \cdot N_0 + \quad N_3' \cdot N_2 \cdot N_1 \cdot N_0) + \dots = \\ &\quad (N_3' \cdot N_2' \cdot N_0) + (N_3' \cdot N_2 \cdot N_0) + \dots = \quad N_3' \cdot N_0 + \dots \end{split}

```

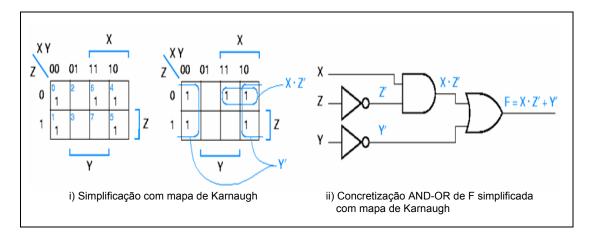

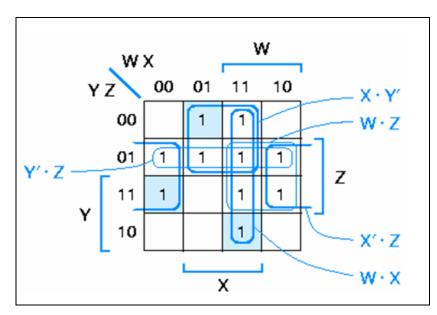

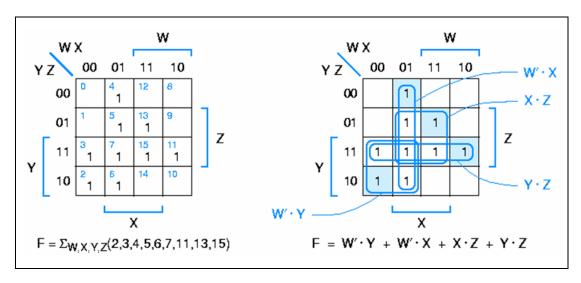

#### 3.3. Mapas de Karnaugh

<u>Não é fácil</u> encontrar o par de termos que participa em cada simplificação. Um **mapa de Karnaugh**\_é uma representação gráfica para a tabela de verdade duma

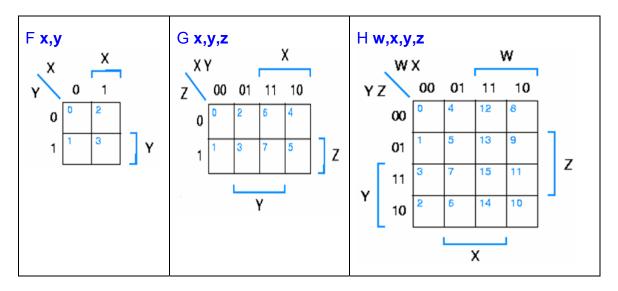

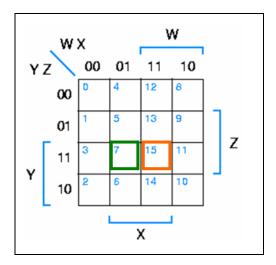

função lógica. O mapa para uma função lógica de **n**-entradas é um array com **2**<sup>n</sup> células, uma por cada mintermo (ver a figura seguinte para os casos n=2, 3 e 4).

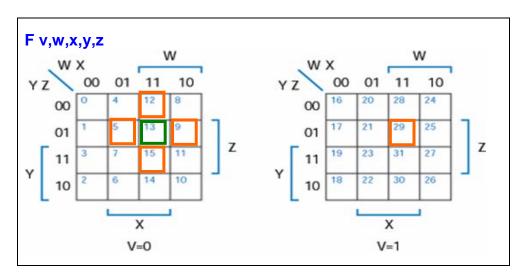

Os mapas de Karnaugh que se utilizam para representar funções com 5 e 6 variáveis não são tão adequados como os mapas de 2, 3 e 4 variáveis, dado a adjacência ser mais difícil de visualizar. Num mapa de **5 variáveis**, é necessário recorrer a 2 mapas de 4 variáveis colocados um ao lado do outro. Nesta representação, considera-se que um mapa é colocado por cima do outro, de modo a originar um objecto 3-dimensional. Neste caso, cada **célula** é adjacente de **5** células: **4** no mesmo mapa e **1** no outro (ver figura abaixo).

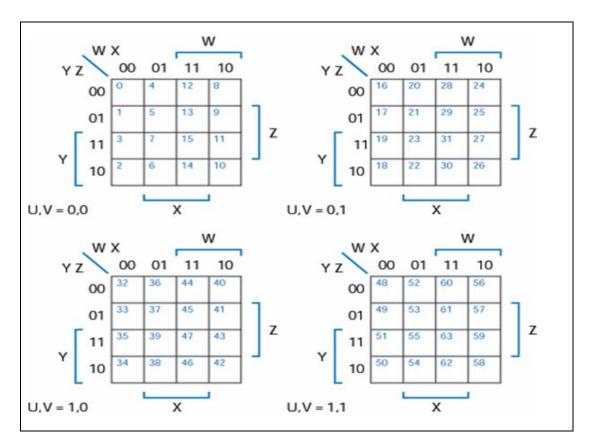

O mapa de Karnaugh que se segue é de 6 variáveis: U, V, W, X, Y e Z.

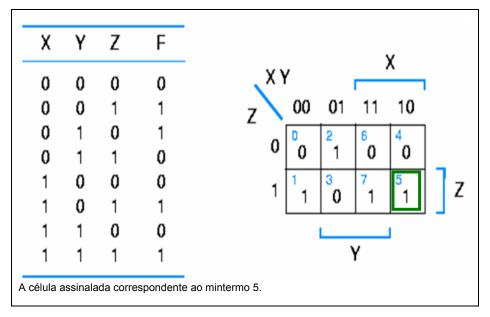

Para representar uma função lógica num mapa de Karnaugh, copiam-se os 1's e 0's da tabela de verdade para as células correspondentes do mapa. Cada célula do mapa corresponde a um mintermo da função.

Na prática, apenas se copiam os 1's ou os 0's (não ambos) para as células, dependendo do tipo de expressão que se pretende obter (SOP ou POS).

#### Q: Porque se usa uma ordenação estranha das linhas e colunas?

Porque assim, cada célula corresponde a uma combinação das entradas que difere apenas numa variável da combinação associada a cada uma das células vizinhas

imediatamente adjacentes. As células **7** e **15**, no mapa de 4 variáveis seguinte, diferem apenas no valor de W. Nos mapas de 3 e 4 variáveis, as células no canto esquerdo (direito) ou superior (inferior) também são vizinhas. As células 8 e 10 no mapa de 4 variáveis diferem apenas no valor de Y.

Uma vez que os pares de células-a-1 adjacentes correspondem a mintermos que diferem apenas numa variável, cada par pode ser combinado num único termo de produto, usando o teorema T10:

produto·Y + produto·Y' = produto

Para o mapa anterior, combinando as células 5 e 7:

$$F = ... + X \cdot Y' \cdot Z + X \cdot Y \cdot Z$$

$$= ... + X \cdot Z$$

Combinando as células 1 e 5:

$$F = X' \cdot Y' \cdot Z + X \cdot Y' \cdot Z + ...$$

= Y' \cdot Z + ...

O mintermo 5 é incluído duas vezes. Não há problema porque X+X=X.

$$F = X \cdot Z + Y' \cdot Z + X' \cdot Y \cdot Z'$$

O procedimento utilizado para combinar células, pode ser estendido para permitir combinar mais do que 2 células-a-1 num único termo.

$$\begin{split} \mathsf{F} &= \sum_{X,Y,Z,} \mathsf{m}(0,1,4,5,6) = \mathsf{X}' \cdot \mathsf{Y}' \cdot \mathsf{Z}' + \mathsf{X}' \cdot \mathsf{Y}' \cdot \mathsf{Z} + \mathsf{X} \cdot \mathsf{Y}' \cdot \mathsf{Z}' + \mathsf{X} \cdot \mathsf{Y}' \cdot \mathsf{Z} + \mathsf{X} \cdot \mathsf{Y}' \cdot \mathsf{Z}' \\ &= [\mathsf{Y}' \cdot (\mathsf{X}' \cdot \mathsf{Z}') + \mathsf{Y}' \cdot (\mathsf{X}' \cdot \mathsf{Z}) + \mathsf{Y}' \cdot (\mathsf{X} \cdot \mathsf{Z}') + \mathsf{Y}' \cdot (\mathsf{X} \cdot \mathsf{Z})] + \mathsf{X} \cdot \mathsf{Y} \cdot \mathsf{Z}' \\ &= \mathsf{Y}' \cdot [(\mathsf{X}' \cdot \mathsf{Z}' + \mathsf{X} \cdot \mathsf{Z}') + (\mathsf{X}' \cdot \mathsf{Z} + \mathsf{X} \cdot \mathsf{Z})] + \mathsf{X} \cdot \mathsf{Y} \cdot \mathsf{Z}' = \mathsf{Y}' \cdot [(\mathsf{X}' + \mathsf{X}) \cdot \mathsf{Z}' + (\mathsf{X}' + \mathsf{X}) \cdot \mathsf{Z}] + \mathsf{X} \cdot \mathsf{Y} \cdot \mathsf{Z}' \\ &= \mathsf{Y}' \cdot (1, \mathsf{Z}' + 1, \mathsf{Z}) + \mathsf{X} \cdot \mathsf{Y} \cdot \mathsf{Z}' = \mathsf{Y}' \cdot (\mathsf{Z}' + \mathsf{Z}) + \mathsf{X} \cdot \mathsf{Y} \cdot \mathsf{Z}' = \mathsf{Y}' \cdot 1 + \mathsf{X} \cdot \mathsf{Y} \cdot \mathsf{Z}' = \mathsf{Y}' + \mathsf{X} \cdot \mathsf{Y} \cdot \mathsf{Z}' \end{split}$$

Generalizando, pode combinar-se  $2^i$  células-a-1 para originar um termo de produto com n-i literais (em que n = número de variáveis). A regra para combinar células-a-1 é descrita por:

Um conjunto de 2<sup>i</sup> células-a-1 pode ser combinado se existirem i variáveis que assumem todas as possíveis combinações (2<sup>i</sup>) dentro desse conjunto, enquanto as restantes n-i variáveis mantêm o mesmo valor em todo o conjunto.

O termo de produto resultante possui n-i literais, em que cada literal é: a variável complementada (se ela aparecer como 0 em todas as células-a-1) ou a variável não complementada (se ela aparecer como 1).

<u>Graficamente</u>, podemos envolver conjuntos rectangulares de 2<sup>n</sup> células-a-1 com um "rectângulo".

A partir de cada rectângulo que envolve células-a-1, obtém-se o correspondente termo de produto:

- Se o rectângulo cobre apenas zonas do mapa em que uma dada variável é 0

(1), então essa variável surge complementada (não complementada) no termo de produto.

- Se o rectângulo cobre zonas do mapa em que uma dada variável é 0 e 1, então essa variável não aparece no termo de produto.

Uma **soma mínima** para a função lógica F é uma expressão do tipo soma de produtos (SOP) para F tal que nenhuma outra expressão SOP para F possui menos termos de produto, e qualquer expressão SOP com o mesmo número de termos de produto possui pelo menos tantos literais como ela. A soma mínima possui o menor número de termos de produto possível (número de portas no 1° nível e número de entradas na porta do 2° nível) e o menor número de literais possível (número de entradas nas portas do 1° nível).

Uma função lógica **P implica** a função lógica **F** ( $P \Rightarrow F$ ) se para cada combinação de entradas em que P=1, então também F=1. Ou seja, F <u>inclui</u> ou <u>cobre</u> P. Um **implicante maior** duma função lógica F é um termo de produto normal P que implica F, de tal modo que se qualquer variável for eliminada de P, então o termo de produto resultante já não implica F. Em termos dum mapa de Karnaugh, um <u>implicante maior</u> de F é um conjunto de células-a-1 envolvido por um rectângulo, de tal modo que se tentarmos aumentá-lo (de modo a cobrir o dobro das células), ele vai cobrir um ou mais O's.

**Teorema do implicante maior**: uma soma mínima é uma soma **de** implicantes maiores.

Para encontrar uma <u>soma mínima</u>, **não é** necessário ter em conta qualquer termo de produto que não seja um implicante maior. A soma de todos os implicantes maiores duma função é designada por **soma completa**. A <u>soma completa</u> **não é** necessariamente uma soma mínima.

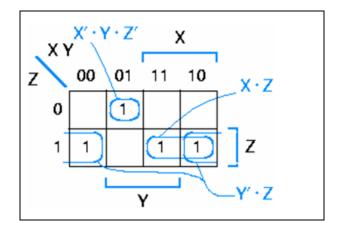

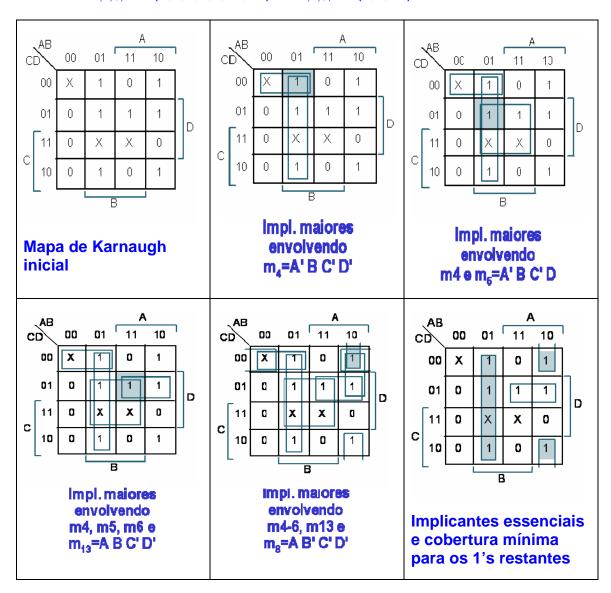

#### Algoritmo: obter a expressão SOP mínima através dum mapa de Karnaugh

#### Passo 1: Marcar os implicantes maiores

Escolher um "1" do ON-set ainda não coberto por qualquer implicante.

Encontrar os grupos de 1's (e X's) adjacentes desse elemento e que possuem a maior dimensão possível. A dimensão tem que ser 2<sup>i</sup>.

Não esquecer a adjacência entre a linha superior e inferior, a coluna esquerda e direita e os cantos.

Repetir o Passo 1 para cada "1" do ON-set, de modo a encontrar todo os implicantes maiores.

#### Passo 2: Marcar os implicantes essenciais

Visitar cada "1" do ON-set. Se o "1" for coberto por um único implicante maior, então este implicante é essencial e aparece na expressão final. Os restantes 1's cobertos pelo implicante não precisam ser revisitados.

Repetir o Passo 2 até que todos os implicantes essenciais tenham sido encontrados.

#### Passo 3: Cobertura adicional

Se existirem 1's não cobertos pelos implicantes essenciais, seleccionar o menor número de implicantes maiores que cobra todos esses 1's. Tentar várias alternativas de cobertura.

Considere a função  $F = \sum_{W,X,Y,Z,} m(1,3,4,5,9,11,12,13,14,15)$ . Esta função possui 5 implicantes maiores. A soma mínima inclui apenas 3 implicantes maiores:  $F = X \cdot Y' + X' \cdot Z + W \cdot X$ . Como se decide quais os implicantes maiores a incluir na expressão minimizada duma função?

Para responder à pergunta anterior, apresentam-se mais algumas definições.

Uma **célula-a-1 distinguida** duma função lógica é uma combinação de entradas que é coberta por um único implicante maior. Um **implicante essencial** duma função lógica é um implicante maior que cobre uma ou mais células-a-1 distinguidas. Os implicantes essenciais <u>têm</u> que aparecer em qualquer soma mínima. O 1º passo na selecção dos implicantes consiste em identificar as células-a-1 distinguidas e incluir os correspondentes implicantes essenciais na soma. Depois, se houver células-a-1 não cobertas pelos implicantes essenciais, falta encontrar a melhor forma de as cobrir.

Exemplo em que todos os implicantes maiores são essenciais:

Exemplo em que nem todos os implicantes maiores são essenciais:

Aplicando o princípio da dualidade, pode minimizar-se expressões do tipo produto de somas (POS) se se funcionar com os 0's do mapa de Karnaugh. Cada 0 do mapa corresponde a um maxtermo. Uma forma mais fácil de encontrar o produto mínimo de F consiste em obter a soma mínima de F'. Obter F' é simples: os 1's de F' são os 0's de F. Após obter a soma mínima para F' (F'sop), complementa-se o

resultado obtido aplicando o teorema de DeMorgan generalizado [T14], de modo a obter o produto mínimo para F (*Fpos*).

Um exemplo:

$$F' = X \cdot Y' + X' \cdot Z + W \cdot X$$

$$F = (X'+Y) \cdot (X+Z') \cdot (W'+X')$$

Por vezes, não interessa qual é o valor da saída da função para certas combinações das entradas. A estas saídas chama-se **don't cares**.

Um exemplo: um detector de números primos em que a entrada *N* com 4-bits é sempre um dígito BCD, ou seja, os mintermos 10-15 nunca ocorrem.

$$F = \sum_{N3,N2,N1,N0} m (1,2,3,5,7) + \sum_{N3,N2,N1,N0} d (10,11,12,13,14,15)$$

Ao introduzir *don't cares* (X's), o procedimento usado para envolver os conjuntos de 1's com rectângulos é alterado do seguinte modo:

- Permite-se que os X's sejam incluídos nos conjuntos de 1's a envolver com rectângulos, para formar conjuntos tão grandes quanto possível. Desta forma reduz-se o número de variáveis nos implicantes maiores que lhe correspondem.

- Não se considera qualquer conjunto que contenha apenas X's. Incluir na função os termos de produto formados a partir de X's aumentaria desnecessariamente o seu custo, ou seja, a função ficaria menos minimizada.

O resto do procedimento mantém-se válido. Por exemplo:

- Visitam-se apenas as células-a-1distinguidas e não as células-a-X distinguidas.

- Inclui-se na função simplificada apenas (i) os implicantes essenciais que correspondem a esses 1's e (ii) outros implicantes maiores que sejam necessários para cobrir todos os 1's do mapa.

Apresenta-se agora, como exemplo, a simplificação da função:

$F = \sum_{A,B,C,D} m (4,5,6,8,9,10,13) + \sum_{A,B,C,D} d (0,7,15)$

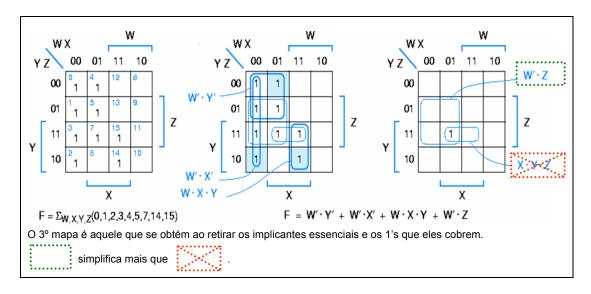

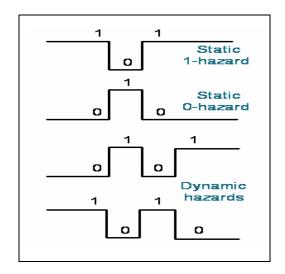

#### 3.4. Hazards

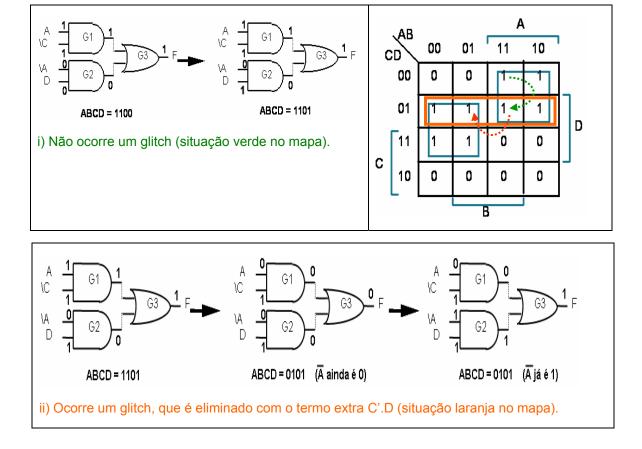

Devido aos atrasos nos componentes electrónicos, um circuito pode originar um *glitch*. Um *glitch* é uma variação de curta duração no valor duma saída, quando não se espera nenhuma variação. Designa-se de *hazard* a situação em que existe a possibilidade de o circuito gerar um *glitch*. Ocorre um *hazard* estático quando existe a possibilidade de uma saída sofrer uma transição momentânea em condições em que se esperava que ela se mantivesse inalterada. Ocorre um *hazard* dinâmico quando for possível uma saída mudar mais do que uma vez, em condições em que se esperava que ela tivesse uma única transição (de  $0 \rightarrow 1$  ou de  $1 \rightarrow 0$ ).

Um *hazard* num 1 (0) estático é um par de combinações de entradas que diferem apenas numa variável de entrada e em que ambas produzem 1 (0) na saída, de tal modo que pode ocorrer um 0 (1) momentâneo na saída, durante uma transição na variável de entrada que distingue essas combinações.

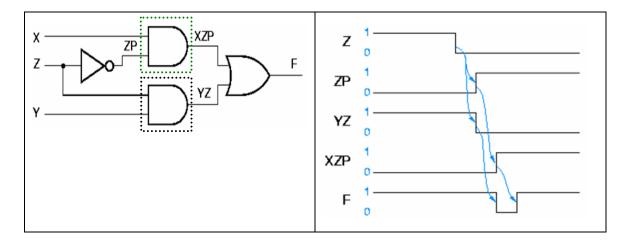

A figura seguinte mostra um circuito que apresenta um *hazard* quando X=Y=1 e Z transita de 1  $\rightarrow$  0.

Os métodos usados para eliminar *hazards* consideram que apenas uma entrada varia em cada instante. Este pressuposto equivale a efectuar um deslocamento através de células vizinhas num mapa de Karnaugh. Os mapas de Karnaugh podem ser usados para detectar *hazards* estáticos em circuitos com estrutura AND-OR ou OR-AND. Num circuito bem projectado e que implemente uma soma de produtos a 2-níveis só podem ocorrer *hazards* em 1's estáticos (não em 0's estáticos).

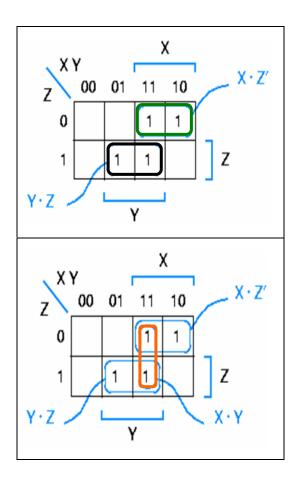

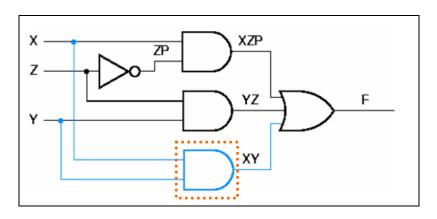

Para o mapa da figura seguinte, como <u>não há um termo de produto que cobre ambas as combinações</u> XYZ=111 e XYZ=110, é possível que se gere um breve *glitch* a 0 na saída (se o AND que muda para 0 o fizer antes do AND que muda para 1). Para eliminar o *hazard*, deve incluir-se no circuito uma porta AND extra.

O circuito que resulta da eliminação do hazard com a porta AND extra é:

Outro exemplo, em que se usam 3 AND's extra para eliminar os hazards estáticos:

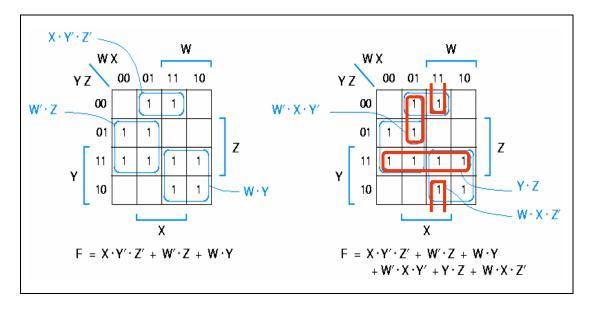

Para terminar, apresenta-se mais um exemplo, em que se mostra a ocorrência e eliminação de um *glitch* na função  $F = \sum_{A,B,C,D} (1,3,5,7,8,9,12,13)$ .

#### 4. VHDL

O VHDL foi desenvolvido na década de 80 pelo DoD e pelo IEEE. VHDL é um acrónimo de VHSIC Hardware Description Language; VHSIC é um acrónimo de Very High Speed Integrated Circuit.

O VHDL possui as seguintes características:

- Os projectos devem ser decompostos de forma hierárquica.

- Cada elemento dum projecto possui uma interface e uma especificação do seu comportamento.

- A especificação dum comportamento pode usar um algoritmo ou uma estrutura para definir o modo de operação do elemento.

- Pode modelar concorrência, temporização e o conceito de relógio (clocking).

- Permite **simular** a operação lógica e o comportamento temporal dum projecto.

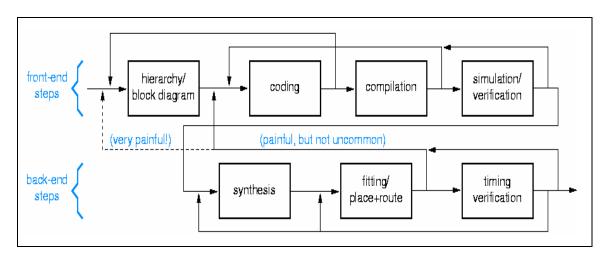

## 4.1. Fluxo de projecto

O VHDL começou por ser uma linguagem de **documentação** e **modelação**, que permitia especificar e simular o comportamento dos projectos. Actualmente existem **ferramentas de síntese** comerciais que geram a estrutura dos circuitos lógicos directamente a partir de especificações em VHDL.

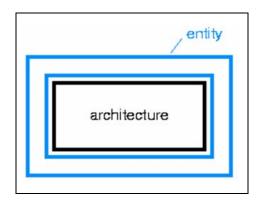

## 4.2. Entidades e arquitecturas

O VHDL foi desenvolvido tendo em consideração muitos dos princípios da programação estruturada. Muitas ideias do VHDL foram importadas do Pascal e do Ada. Uma das ideias chave do VHDL é a utilização de interfaces que definem a fronteira dos módulos (de hardware), ao mesmo tempo que escondem os pormenores relativos ao seu interior. Em VHDL, a entidade (entity) é uma declaração das entradas e saídas dum módulo. A arquitectura (architecture) é uma descrição detalhada da estrutura ou comportamento interno dum módulo.

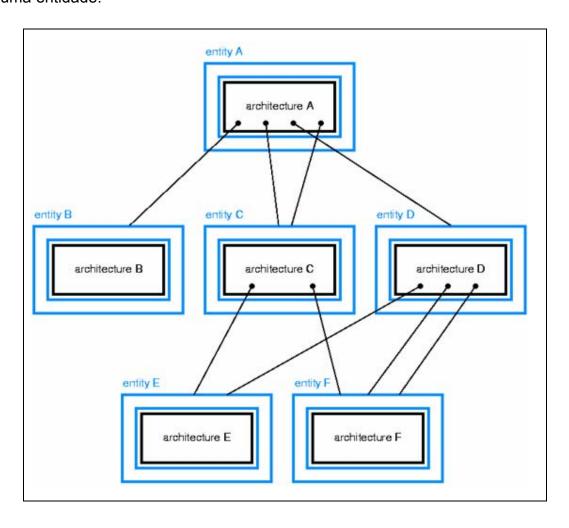

Uma arquitectura pode usar outras entidades. Uma arquitectura de nível superior pode usar uma entidade de nível inferior várias vezes. Várias arquitecturas de nível superior podem usar a mesma entidade de nível inferior. Estas facilidades são o suporte básico para projectar sistemas de forma hierárquica.

As **configurações** definem qual a arquitectura a usar em cada ocorrência duma entidade.

Num ficheiro texto, contendo código VHDL, a declaração da <u>entidade</u> e a definição da <u>arquitectura</u> estão separadas.

```

entity Inhibit is

port (X,Y: in BIT;

Z: out BIT);

end Inhibit;

architecture Inhibit_arch of Inhibit is

begin

Z <= '1' when X='1' and Y='0' else '0';

end Inhibit_arch;</pre>

text file (e.g., mydesign.vhd)

architecture declaration

architecture definition

text file (e.g., mydesign.vhd)

entity declaration

architecture definition

architectur

```

A linguagem não distingue maiúsculas de minúsculas. Os <u>comentários</u> começam com 2 hífenes "--" e terminam no fim da linha. O VHDL possui <u>palavras</u> (chave) <u>reservadas</u>: port, is, in, out, begin, end, entity, architecture, if, case, ...

A sintaxe da declaração duma entidade é:

```

entity entity-name is

port(signal-names : mode signal-type;

signal-names : mode signal-type;

signal-names : mode signal-type);

end entity-name;

```

Numa entidade, mode indica qual a direcção dum porto da interface. Um **porto** é uma entrada, saída ou entrada/saída dum módulo. As possibilidades para a direcção dum porto são:

in: entrada da entidade; out: saída da entidade;

buffer: saída da entidade (o seu valor pode ser lido dentro da arquitectura);

inout: entrada e saída da entidade.

Nesta declaração, signal-type designa um tipo de sinal predefinido ou um tipo definido pelo utilizador.

**Sinal** é o objecto primário utilizado para descrever sistemas, equivale a um "fio" físico e tem um historial de valores passados associado. Os sinais funcionam como canais de comunicação entre instruções concorrentes. A **sintaxe** da declaração dum **sinal** é:

signal nome sinal: tipo sinal:= valor inicial opcional;

Os sinais podem ser declarados explicitamente na declaração dum *package*, numa arquitectura, num bloco ou num subprograma. A declaração dum porto duma entidade é uma declaração implícita dum sinal.

Variável é similar a um sinal, mas sem o equivalente físico e sem o historial de valores.

A sintaxe da definição duma arquitectura é:

```

architecture architecture-name of entity-name is

type declarations

signal declarations

constant declarations

function definitions

procedure definitions

component declarations

begin

concurrent-statement

concurrent-statement

end architecture-name;

```

As declarações (tipos, sinais,...,componentes) podem surgir por qualquer ordem. Em "signal declarations" definem-se os sinais internos à arquitectura.

## 4.3. Tipos

Qualquer sinal, variável e constante tem um tipo associado. O **tipo** especifica o conjunto de valores permitidos a um objecto e os operadores que podem ser aplicados a esse objecto. Esta definição de tipo equivalente a um tipo de dados abstracto, um conceito similar ao de classe em OO. VHDL é uma linguagem fortemente "tipada" mas que possui apenas os seguintes tipos predefinidos:

```

bit character severity_level

bit_vector integer string

boolean real time

```

- integer inclui os inteiros no intervalo -2.147.483.647 a +2.147.483.647

- boolean possui 2 valores: true e false

- character inclui os caracteres do conjunto ISO 8-bit.

A tabela em baixo inclui os <u>operadores</u> predefinidos para os tipos **integer** e **boolean**. A funcionalidade dos operadores menos triviais, rem e mod, é agora descrita:

```

A rem B \rightarrow módulo = A – int(A/B)*B e sinal = sinal de A

A mod B \rightarrow módulo = A – int(A/B)*B [quando A e B são do mesmo sinal]

módulo = A + ceil(|A/B|)*B [quando A e B são de sinais diferentes]

sinal = sinal de B

```

| in  | teger <b>Operators</b> | boolean <b>Operators</b> |                 |  |  |

|-----|------------------------|--------------------------|-----------------|--|--|

| +   | addition               | and                      | AND             |  |  |

| -   | subtraction            | or                       | OR              |  |  |

| *   | multiplication         | nand                     | NAND            |  |  |

| /   | division               | nor                      | NOR             |  |  |

| mod | modulo division        | xor                      | Exclusive OR    |  |  |

| rem | modulo remainder       | xnor                     | Exclusive NOR   |  |  |

| abs | absolute value         | not                      | complementation |  |  |

| * * | exponentiation         |                          |                 |  |  |

Os <u>tipos definidos pelo utilizador</u> são comuns em VHDL. Um <u>tipo enumerado</u> é definido através duma lista de valores permitidos.

```

type type-name is (value-list);

subtype subtype-name is type-name start to end;

subtype subtype-name is type-name start downto end;

constant constant-name: type-name := value;

```

Os 9 níveis permitidos pelo tipo STD\_LOGIC são:

```

type STD_ULOGIC is (

'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-'); -- Don't care

subtype STD_LOGIC is resolved STD_ULOGIC;

```

## Outros exemplos são:

- type traffic\_light\_state is (reset, stop, start, go);

- **subtype** int32 **is integer range** 31 downto 0;

- constant BUS\_SIZE: integer := 32;

O utilizador também pode definir **arrays** usando as palavras-chave **to**, **downto** e **range** para definir a dimensão. Um array é um conjunto ordenado de elementos do mesmo tipo.

```

type type-name is array(start to end) of element-type;

type type-name is array(start downto end) of element-type;

type type-name is array(range-type) of element-type;

type type-name is array(range-type range start to end) of element-type;

type type-name is array(range-type range start downto end) of element-type;

type monthly_count is array (1 to 12) of integer;

type byte is array (7 downto 0) of STD_LOGIC;

constant NORD_LEN: integer := 32;

type word is array (NORD_LEN-1 downto 0) of STD_LOGIC;

constant NUM_REGS: integer := 8;

type reg_file is array (1 to NUM_REGS) of word;

type statecount is array (traffic_light_state) of integer;

```

O conteúdo dos elementos dum *array* pode ser especificado **por posição**, colocando a lista de valores a atribuir entre parênteses:

```

B := ('1','1','0','1','1','0','0','1'); -- tipo byte

```

O conteúdo do *array* também pode ser especificado **usando índices**:

```

W := (0 = >'0', 3 = >'0', 9 = >'0', others = >'1'); -- tipo word

```

O conteúdo dum array STD LOGIC pode ser especificado usando strings:

```

B := "11011001";

W := "0110111110111111";

```

Também se pode especificar uma parcela dum array.

```

B(2 \text{ to } 4) := "101"; W(9 \text{ downto } 0) := "0101011010";

```

Pode juntar-se arrays usando o operador de concatenação (&):

```

'0'&'1'&"1Z" é equivalente a "011Z".

B(6 downto 0)& B(7) equivale a rodar o array B um 1-bit à esquerda.

```

#### 4.4. Funções e procedimentos

Uma <u>função</u> aceita um conjunto de argumentos e devolve um resultado. Tanto os argumentos como o resultado devem ter um <u>tipo</u>. O corpo da função é um

conjunto de instruções executadas em <u>sequência</u>. A sintaxe da definição de função é:

```

function function-name (

signal-names : signal-type;

signal-names : signal-type;

signal-names : signal-type

) return return-type is

type declarations

constant declarations

variable declarations

function definitions

procedure definitions

begin

sequential-statement

end function-name;

```

Exemplo de definição e utilização duma função ButNot:

```

architecture Inhibit_archf of Inhibit is

function ButNot (A, B: bit) return bit is

begin

if B = '0' then return A;

else return '0';

end if;

end ButNot;

begin

Z <= ButNot(X,Y);

end Inhibit_archf;</pre>

```

Normalmente é necessário converter um sinal de um tipo para outro. Usando o tipo de array

```

type STD LOGIC VECTOR is array (natural range <>) of STD LOGIC;

```

apresentam-se a seguir 2 funções de conversão de tipos: de **std\_logic** para **inteiro** e de **inteiro** para **std\_logic**.

```

function CONV_INTEGER (X: STD_LOGIC_VECTOR) return INTEGER is

variable RESULT: INTEGER;

begin

RESULT := 0;

for i in X'range loop

RESULT := RESULT * 2;

case X(i) is

when '0' | 'L' => null;

when '1' | 'H' => RESULT := RESULT + 1;

when others => null;

end case;

end loop;

return RESULT;

end CONV_INTEGER;

```

```

function CONV_STD_LOGIC_VECTOR (ARG: INTEGER; SIZE: INTEGER)

return STD_LOGIC_VECTOR is

variable result: STD_LOGIC_VECTOR (SIZE-1 downto 0);

variable temp: integer;

begin

temp := ARG;

for i in 0 to SIZE-1 loop

if (temp mod 2) = 1 then result(i) := '1';

else result(i) := '0';

end if;

temp := temp / 2;

end loop;

return result;

end;

```

Um **procedimento** é idêntico a uma função, mas não devolve um resultado. Enquanto a invocação duma função pode ser usada em vez duma expressão, a invocação dum procedimento pode ser usada em vez duma instrução. Como os argumentos dum procedimento podem ter uma direcção do tipo **out** ou **inout**, é possível um procedimento "devolver" resultado(s).

### 4.5. Bibliotecas e packages

Uma biblioteca é o local onde o compilador de VHDL guarda a informação relativa a um determinado projecto (intermédia, da simulação e da síntese). Para qualquer projecto, o compilador cria e utiliza a biblioteca <u>work</u>. Um projecto pode usar múltiplos ficheiros, cada um com unidades (entidades / arquitecturas) diferentes. Quando um ficheiro é compilado, os resultados são guardados na biblioteca work. Nem toda a informação necessária a um projecto deve estar na biblioteca work. O projectista pode recorrer a definições ou funções que são comuns a vários projectos (por exemplo, incluídas na biblioteca IEEE). Um projecto pode especificar que vai usar bibliotecas que contêm definições partilháveis.

## Um exemplo: library ieee;

A especificação duma biblioteca permite aceder a todas as entidades e arquitecturas guardadas nessa biblioteca, mas não dá acesso aos tipos, subtipos, funções, procedimentos,... Um *package* é um ficheiro com definições de objectos (sinais, tipos, constantes, funções, procedimentos, componentes) que podem ser utilizados nos projectos. A cláusula seguinte permite a um projecto usar todas as definições do *package standard* 1164 do IEEE:

use ieee.std\_logic\_1164.all;

A sintaxe da definição dum package é:

package package-name is

type declarations

signal declarations

constant declarations

component declarations

function declarations

procedure declarations

end package-name;

package body package-name is

type declarations

constant declarations

function definitions

procedure definitions

end package-name;

# 4.6. Projecto estrutural

O corpo duma arquitectura é uma série de **instruções concorrentes**. Cada instrução concorrente é executada em simultâneo com as outras instruções concorrentes incluídas no mesmo corpo de arquitectura. As instruções concorrentes são necessárias para simular o modo paralelo em que os elementos de *hardware* funcionam. A instrução concorrente mais elementar é a instanciação dum **componente**. Apresenta-se a seguir a sintaxe da instanciação dum componente:

```

label: component-name port map (signal), signal2, ..., signaln);

label: component-name port map (port) => signal), port2 => signal2, ..., portn => signaln);

```

A primeira linha da figura anterior estabelece um mapeamento entre portos e sinais externos **por posição**, enquanto a segunda linha define um mapeamento

**explícito** entre portos e sinais externos. Ainda nesta figura, component-name é o nome duma entidade definida anteriormente.

Por cada instanciação dum componente é criada uma instância da entidade respectiva. Antes de instanciar um componente ele tem que ser declarado na parte declarativa da arquitectura usando o construtor **component**. A declaração dum componente é essencialmente o mesmo que a declaração da interface da entidade correspondente. A sintaxe da declaração dum componente é:

Os componentes usados numa arquitectura podem ter sido definidos anteriormente no projecto em causa, ou podem estar definidos numa biblioteca.

O exemplo que se segue apresenta a descrição estrutural do detector de números primos.

```

library IEEE;

use IEEE.std_logic_1164.all;

entity prime is

port ( N: in STD_LOGIC_VECTOR (3 downto 0); F: out STD_LOGIC );

end prime;

architecture primel_arch of prime is

signal N3_L, N2_L, N1_L: STD_LOGIC;

signal N3L NO, N3L N2L N1, N2L N1 NO, N2 N1L NO: STD LOGIC;

component INV port (I: in STD_LOGIC; O: out STD_LOGIC); end component;

component AND2 port (IO, I1: in STD_LOGIC; O: out STD_LOGIC); end component;

component AND3 port (I0, I1, I2: in STD_LOGIC; O: out STD_LOGIC); end component;

component OR4 port (I0,I1,I2,I3: in STD_LOGIC; O:out STD_LOGIC); end component;

begin

U1: INV port map (N(3), N3_L);

U2: INV port map (N(2), N2_L);

U3: INV port map (N(1), N1_L);

U4: AND2 port map (N3_L, N(0), N3L_N0);

U5: AND3 port map (N3_L, N2_L, N(1), N3L_N2L_N1);

U6: AND3 port map (N2_L, N(1), N(0), N2L_N1_N0);

U7: AND3 port map (N(2), N1_L, N(0), N2_N1L_N0);

U8: OR4 port map (N3L_N0, N3L_N2L_N1, N2L_N1_N0, N2_N1L_N0, F);

end prime1_arch;

(i) sinais internos:

(ii) declaração de componentes;

(iii) instanciação de componentes.

```

Uma arquitectura que utiliza componentes é uma **descrição estrutural**, uma vez que descreve a estrutura de interligação entre os sinais e as entidades que concretizam essa entidade. A instrução **generate** permite criar estruturas repetitivas. A sintaxe do ciclo **for...generate** é:

```

label: for identifier in range generate

concurrent-statement

end generate;

identifier – é uma variável implicitamente declarada.

```

Exemplo de um inversor de 8 bits descrito com um ciclo for ... generate.

```

library IEEE;

use IEEE.std_logic_1164.all;

entity inv8 is

port ( X: in STD_LOGIC_VECTOR (1 to 8);

Y: out STD_LOGIC_VECTOR (1 to 8) );

end inv8;

architecture inv8_arch of inv8 is

component INV port (I: in STD_LOGIC; O:out STD_LOGIC); end component;

begin

g1: for b in 1 to 8 generate

U1: INV port map (X(b), Y(b));

end generate;

end inv8_arch;

```

Pode definir-se **constantes genéricas** na declaração duma entidade. A próxima figura mostra a sintaxe da declaração duma entidade usando constantes genéricas. As constantes genéricas permitem definir uma <u>entidade</u> parametrizada.

```

entity entity-name is

generic (constant-names: constant-type;

constant-names: constant-type;

constant-names: constant-type);

port (signal-names: mode signal-type;

signal-names: mode signal-type;

signal-names: mode signal-type);

end entity-name;

```

Cada constante pode ser usada dentro da arquitectura em que é declarada e a atribuição dum valor a essa constante ocorre apenas quando a entidade for instanciada noutra arquitectura. Ao instanciar um componente, para atribuir valores às constantes genéricas utiliza-se uma cláusula generic map.

Circuito inversor dos bits dum barramento de largura parametrizável (**WID**) e descrito com um ciclo **for ... generate** (ver figura).

Descreve-se agora a entidade que instancia o inversor de barramento com 3 valores de WID: 8,16 e 32,

```

library IEEE;

use IEEE.std_logic_1164.all;

entity businv_example is

port ( IN8: in STD_LOGIC_VECTOR (7 downto 0);

OUT8: out STD_LOGIC_VECTOR (7 downto 0);

IN16: in STD_LOGIC_VECTOR (15 downto 0);

OUT16: out STD LOGIC VECTOR (15 downto 0);

IN32: in STD_LOGIC_VECTOR (31 downto 0);

OUT32: out STD_LOGIC_VECTOR (31 downto 0) );

end businv_example;

architecture businv_ex_arch of businv_example is

component businy

generic (WIDTH: positive);

port ( X: in STD_LOGIC_VECTOR (WIDTH-1 downto 0);

Y: out STD_LOGIC_VECTOR (WIDTH-1 downto 0) );

end component;

begin

U1: businv generic map (WIDTH=>8) port map (IN8, OUT8);

U2: businv generic map (WIDTH=>16) port map (IN16, OUT16);

U3: businv generic map (WIDTH=>32) port map (IN32, OUT32);

end businv_ex_arch;

```

### 4.7. Projecto fluxo de dados (dataflow)

Se uma arquitectura emprega apenas instruções concorrentes, o que ela descreve é o fluxo de dados e as operações que são aplicadas aos dados dentro do circuito. Este estilo de descrição é designado por **fluxo de dados**. Dois tipos de instrução concorrente que se usam numa descrição fluxo de dados são:

- Atribuição concorrente dum valor a um sinal a largura e o tipo de ambos os lados da instrução têm que ser compatíveis;

- Atribuição concorrente e condicional dum valor a um sinal.

A sintaxe dos 2 tipos de atribuição concorrente é:

Exemplo de uma descrição fluxo de dados para o detector de números primos, usando operadores predefinidos como **and**, **or**, **not** e **atribuições simples**.

```

architecture prime2_arch of prime is

signal N3L_N0, N3L_N2L_N1, N2L_N1_N0, N2_N1L_N0: STD_LOGIC;

begin

N3L_N0

\leq not N(3)

and N(0);

N3L_N2L_N1 \le not N(3) and not N(2) and

N(1)

N2L_N1_N0

not N(2) and

N(1) and N(0);

N2_N1L_N0

N(2) and not N(1) and N(0);

<=

F <= N3L_N0 or N3L_N2L_N1 or N2L_N1_N0 or N2_N1L_N0;

end prime2_arch;

```

Exemplo de uma descrição fluxo de dados usando atribuições condicionais.

```

architecture prime3_arch of prime is

signal N3L_N0, N3L_N2L_N1, N2L_N1_N0, N2_N1L_N0: STD_LOGIC;

begin

N3L_N0 <= '1' when N(3)='0' and N(0)='1' else '0';

N3L_N2L_N1 <= '1' when N(3)='0' and N(2)='0' and N(1)='1' else '0';

N2L_N1_N0 <= '1' when N(2)='0' and N(1)='1' and N(0)='1' else '0';

N2_N1L_N0 <= '1' when N(2)='1' and N(1)='0' and N(0)='1' else '0';

E <= N3L_N0 or N3L_N2L_N1 or N2L_N1_N0 or N2_N1L_N0;

end prime3_arch;

```

Outro tipo de instrução concorrente é a **atribuição selectiva a um sinal**, idêntica a um construtor CASE. A sintaxe da atribuição selectiva é:

```

with expression select

signal-name <= signal-value when choices,

signal-value when choices,

signal-value when choices;

```

Exemplo de uma descrição fluxo de dados para o detector de números primos usando uma **atribuição selectiva ao sinal F**. As várias escolhas devem ser mutuamente exclusivas e cobrir todos os casos.

```

architecture prime4_arch of prime is

begin

with N select

F <= '1' when "0001",

'1' when "0011" | "0101" | "0111",

'1' when "1011" | "1101",

'0' when others;

end prime4_arch;

```

O código seguinte constitui outra descrição fluxo de dados para o mesmo detector.

## 4.8. Projecto comportamental (ou funcional)

O principal construtor usado em descrições comportamentais é o **processo**, o qual consiste numa série de instruções sequenciais que são executadas em paralelo com outras instruções e processos concorrentes. Um processo tem um tempo de simulação nulo. Um processo em VHDL é assim uma instrução concorrente, com sintaxe:

```

process (signal-name, signal-name, ..., signal-name)

type declarations

variable declarations

constant declarations

function definitions

procedure definitions

begin

sequential-statement

sequential-statement

end process;

```

Um processo <u>não pode declarar sinais</u>, apenas variáveis, utilizadas para guardar informação relativa ao estado do processo. A sintaxe da definição duma variável é:

#### variable nome\_variavel: tipo\_variavel;

Um processo em VHDL está num de 2 estados: em <u>execução ou suspenso</u>. A lista de sinais incluída na definição dum processo (**lista de sensibilidade**) determina <u>quando</u> é que ele <u>é executado</u>. Um processo está inicialmente suspenso. Quando um sinal da lista de sensibilidade muda de valor, o processo retoma a execução, desde a 1ª instrução até à última. Se um sinal da lista de sensibilidade mudar de valor durante a execução do processo, este será executado outra vez. A execução continua até o processo terminar a execução sem que nenhum destes sinais tenha mudado de valor. Na simulação, a execução do corpo dum processo (até ele ser suspenso) decorre num tempo de simulação nulo. Após ter retomado a execução, um processo correctamente escrito será suspenso ao fim de algumas execuções. Contudo, é possível escrever (incorrectamente) um processo que nunca é suspenso.

Um exemplo: um processo com uma única instrução "X <= not X;" e uma lista de sensibilidade igual a "(X)". Como X muda em cada execução, o processo executa indefinidamente num tempo de simulação nulo. Na prática, os simuladores conseguem detectar estas situações e terminar a simulação.

A instrução de <u>atribuição sequencial dum valor a um sinal</u> possui a mesma sintaxe que a versão concorrente, mas ocorre no corpo dum processo em vez de numa arquitectura:

nome-sinal <= expressão;

A instrução de atribuição dum valor a uma variável possui a seguinte sintaxe:

```

nome-variavel := expressão;

```

Exemplo de uma descrição comportamental para o detector de números primos, em que se usa um processo com atribuições a variáveis.

```

architecture prime6_arch of prime6 is

begin

process(N)

variable N3L_N0, N3L_N2L_N1, N2L_N1_N0, N2_N1L_N0: STD_LOGIC;

N3L_N0

:= not N(3)

and N(0);

N3L_N2L_N1 := not N(3) and not N(2) and N(1)

N2L_N1_N0 :=

not N(2) and

N(1) and N(0);

N2_N1L_N0 :=

N(2) and not N(1) and N(0);

E <= N3L_N0 or N3L_N2L_N1 or N2L_N1_N0 or N2_N1L_N0;</pre>

end process;

end prime6_arch;

```

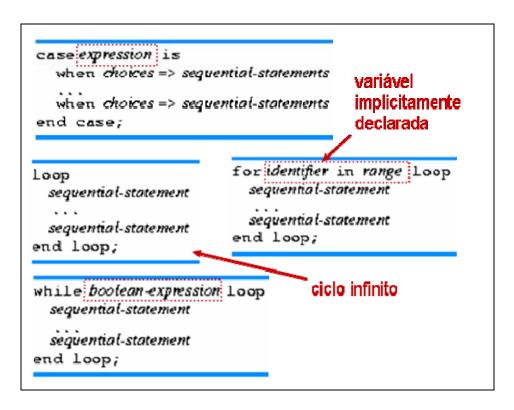

Além da atribuição, pode usar-se outras instruções sequenciais, descritas por alguns dos construtores mais populares, tais como: <u>if</u>, <u>case</u>, <u>loop</u>, <u>for</u> e <u>while</u>. O **case** é mais legível que um <u>if</u> com múltiplas cláusulas if/elsif e pode ser sintetizado de forma mais adequada. As 2 figuras seguintes incluem a sintaxe destes construtores.

```

if boolean-expression then sequential-statement end if;

if boolean-expression then sequential-statement else sequential-statement end if;

if boolean-expression then sequential-statement elsif boolean-expression then sequential-statement elsif boolean-expression then sequential-statement end if;

if boolean-expression then sequential-statement elsif boolean-expression then sequential-statement elsif boolean-expression then sequential-statement elsif boolean-expression then sequential-statement else sequential-statement end if;

```

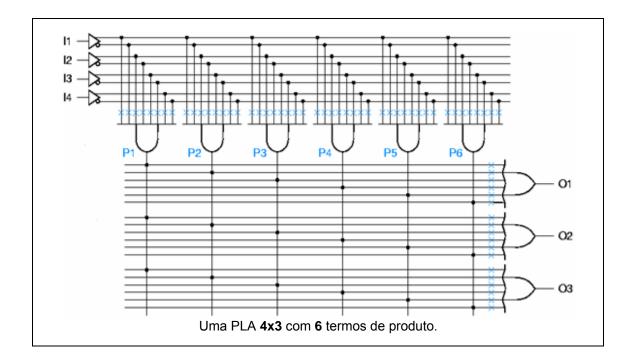

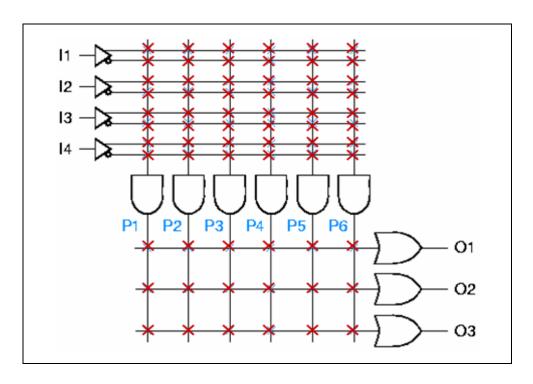

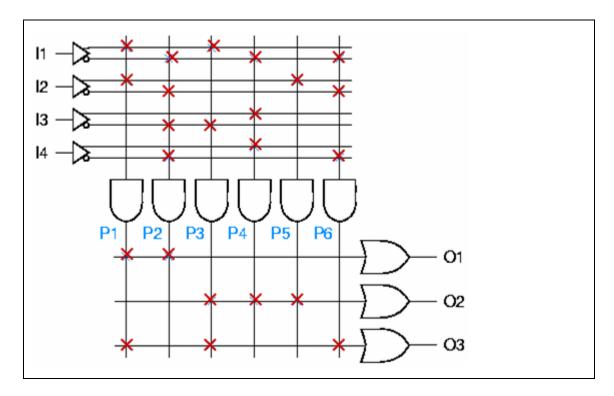

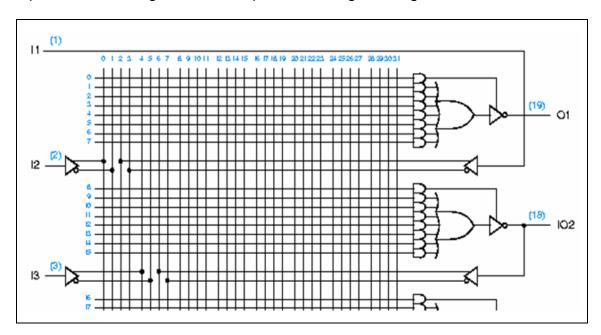

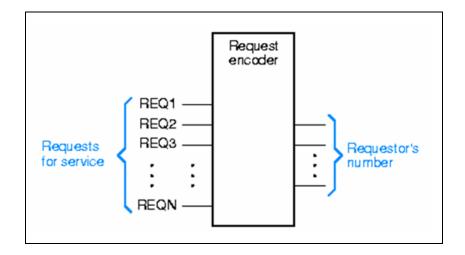

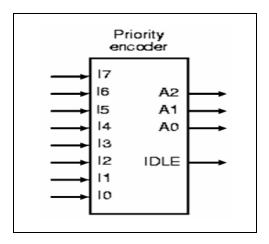

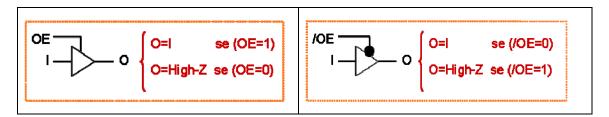

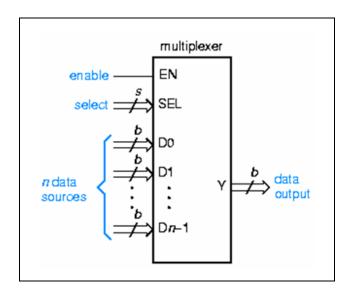

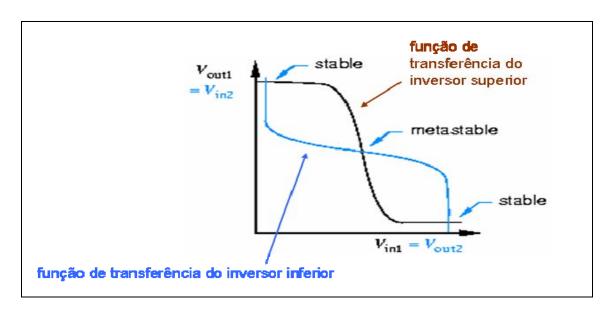

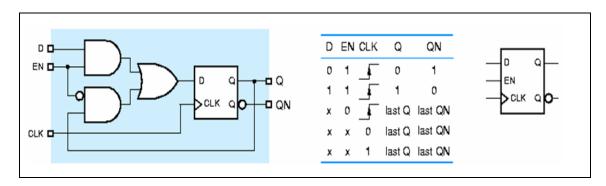

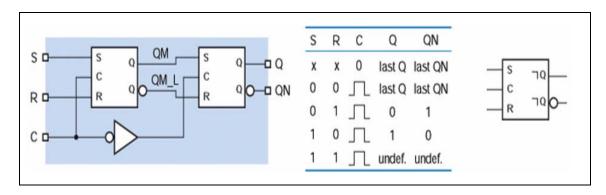

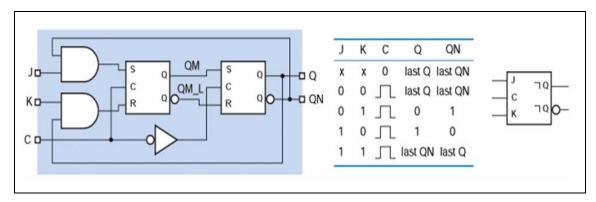

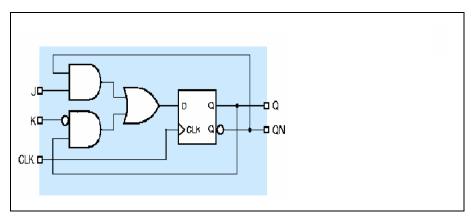

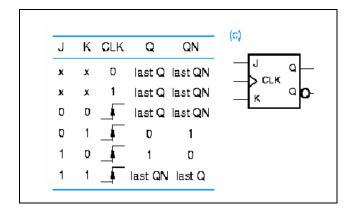

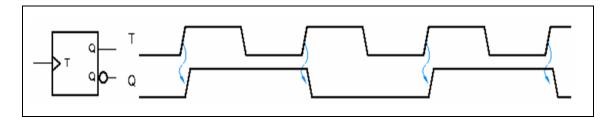

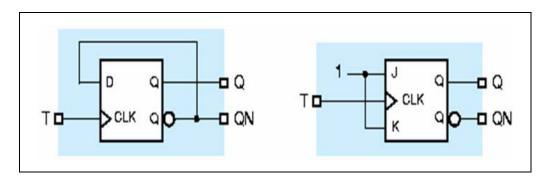

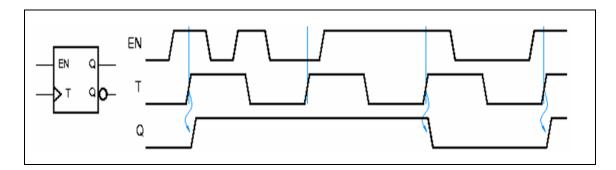

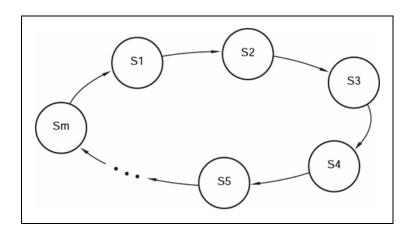

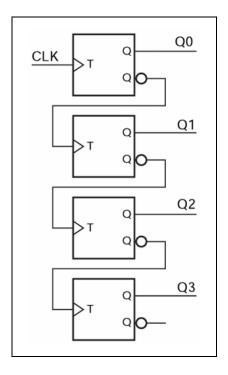

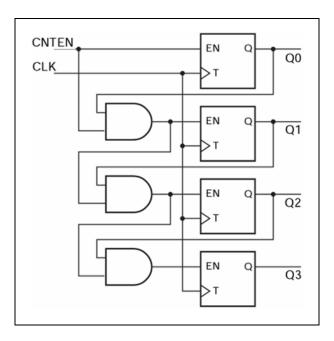

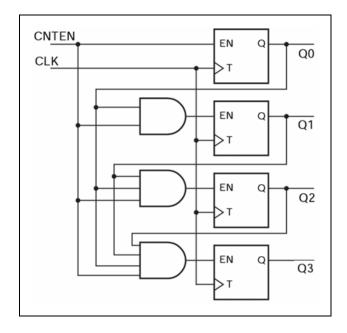

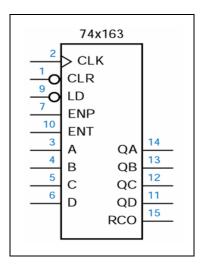

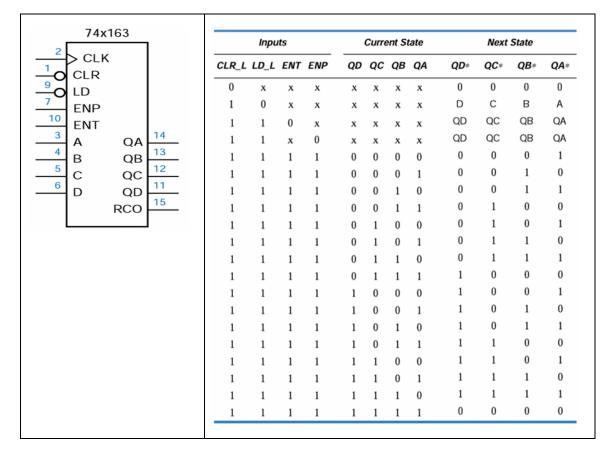

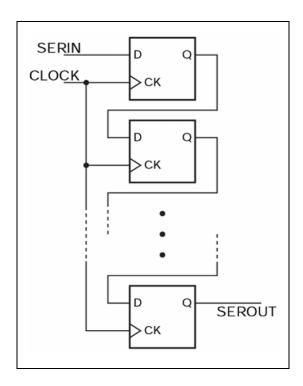

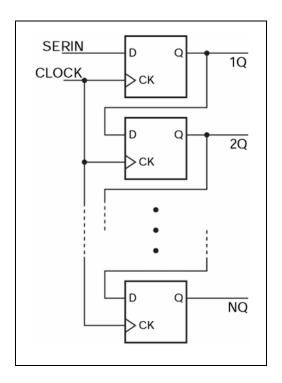

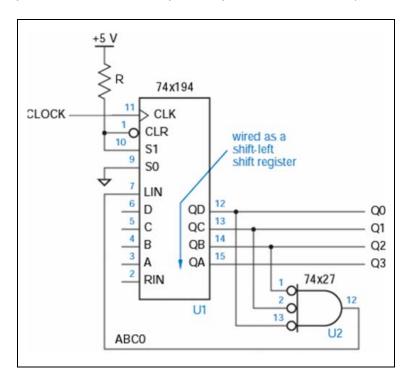

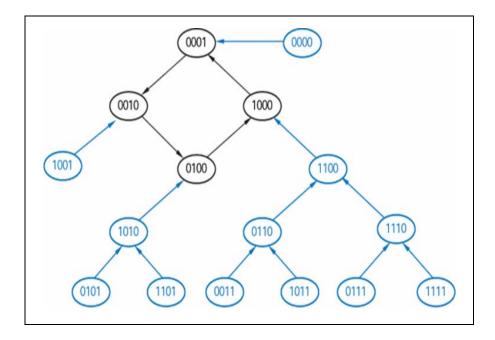

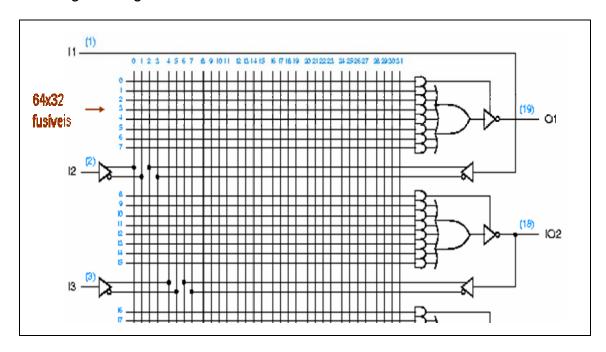

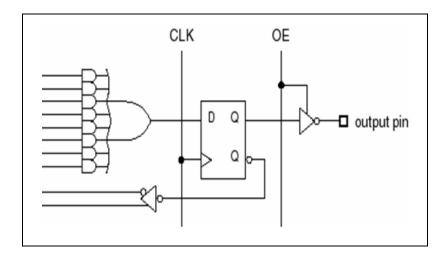

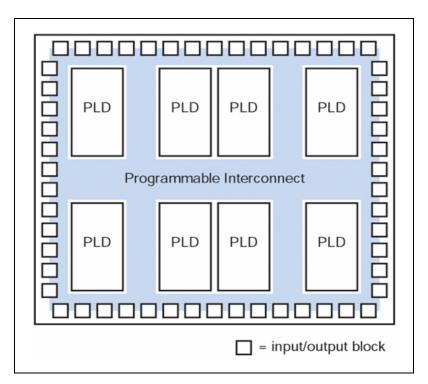

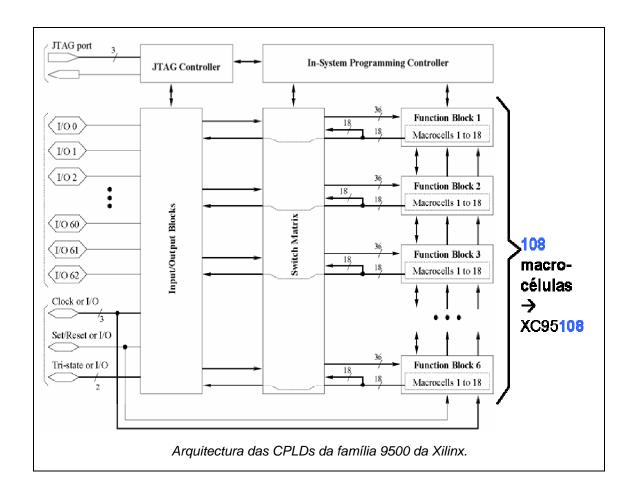

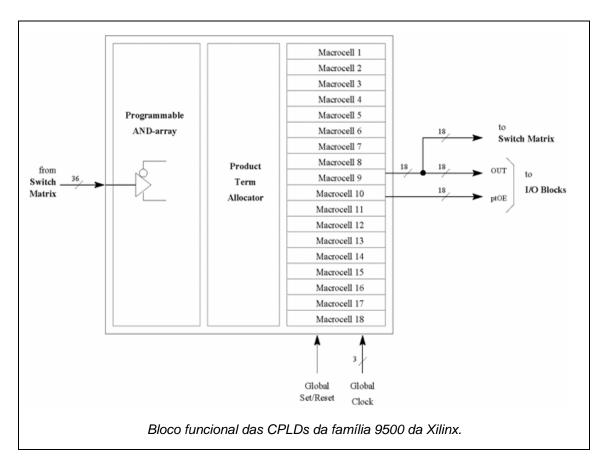

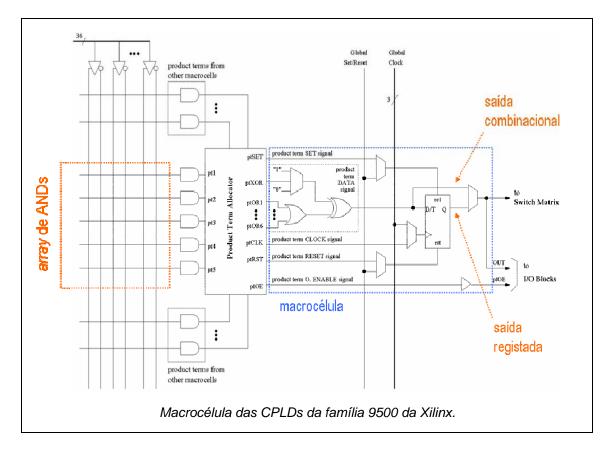

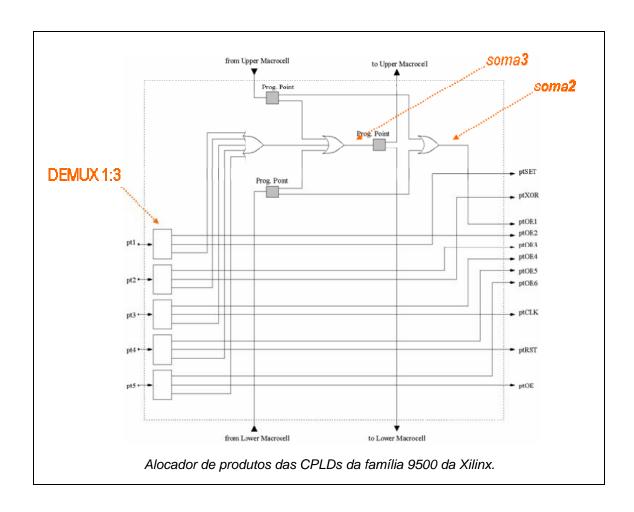

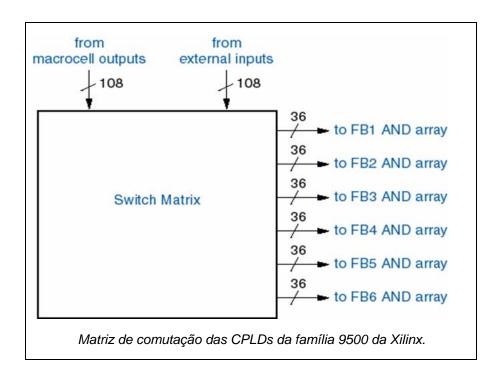

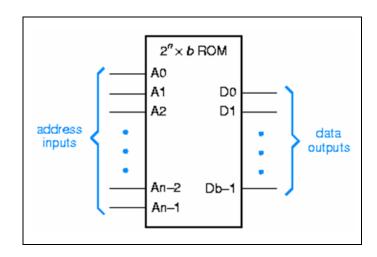

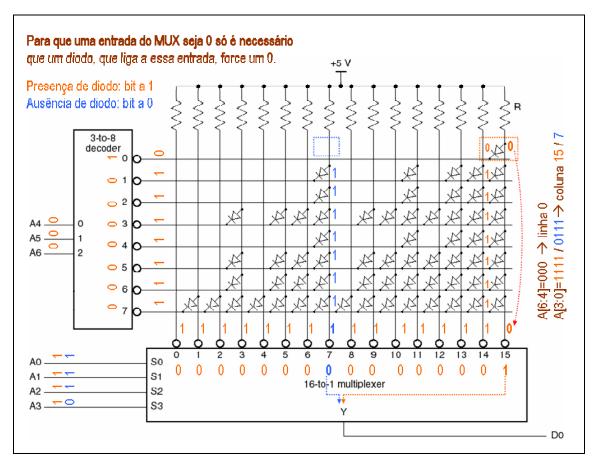

No caso do case, as várias escolhas devem ser mutuamente exclusivas e cobrir todos os casos.